### **TOSHIBA**

### TECHNCAL TRAINING MANUAL

# DATA & GRAPHICS PROJECTOR **P7300U**

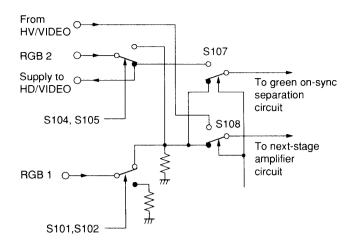

### **CONTENTS**

| SECTION I                             | SECTION IV                                       |

|---------------------------------------|--------------------------------------------------|

| OPTICAL SYSTEM 1-1                    | CONTROL CIRCUIT 4-1                              |

| 1. NECK COMPONENTS 1-2                | 1. OUTLINE                                       |

| 2 FUNCTIONS OF MAJOD                  | 2 INTERNAL SYNC SIGNAL                           |

| COMPONENTS 1-2                        | GENERATION CIRCUIT 4-2                           |

|                                       | 3. TEST PATTERN                                  |

| CECTION II                            | GENERATION CIRCUIT 4-2                           |

| SECTION II                            | 4. VARIOUS DATA 4-8                              |

| POWER SUPPLY                          |                                                  |

| CIRCUIT 2-1                           | SECTION V                                        |

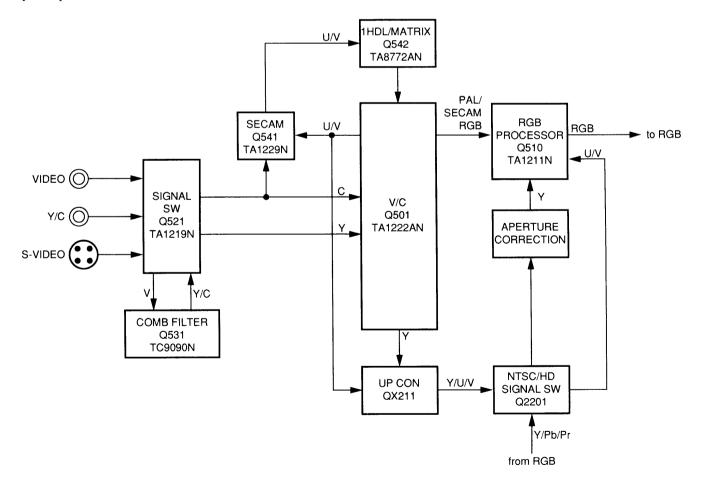

| 1. OUTLINE 2-2                        | <b>VIDEO CIRCUIT 5-1</b>                         |

| 2. P-RECT/HV PC BOARD 2-2             | 1. OUTLINE 5-2                                   |

| 3. POWER-1 PC BOARD 2-6               | 2. FLOW OF SIGNAL 5-2                            |

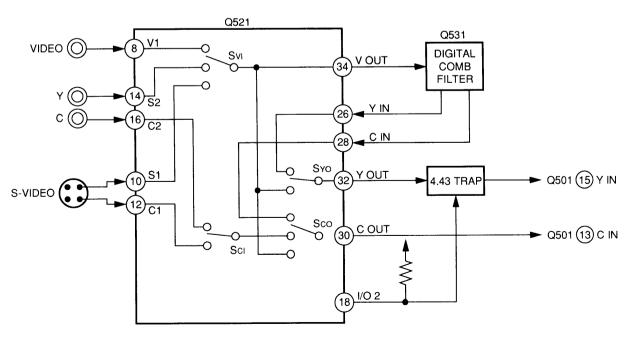

| 4. POWER-2 PC BOARD 2-6               | 3. INPUT SWITCHING CIRCUIT5-3                    |

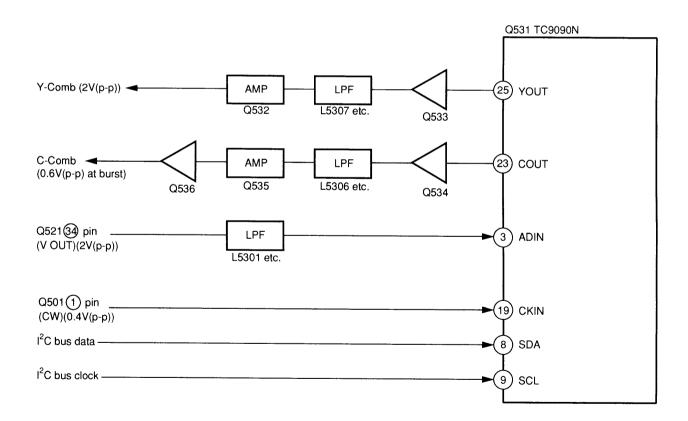

| 5. PROTECTION CIRCUIT 2-7             | 4. DIGITAL COMB FILTER 5-3                       |

| 6. TROUBLESHOOTING2-8                 | 5 PAL/SECAM PROCESSING                           |

|                                       | CIRCUIT 5-6                                      |

| SECTION III                           | 6. UP-CONVERTER CIRCUIT 5-14                     |

| SECTION III                           | 7. NTSC/HDTV PROCESSING                          |

| MICROPROCESSOR                        | CIRCUIT 5-19                                     |

| (CONTROL) 3-1                         | 8. CONTROL SYSTEM 5-24                           |

| 1. OUTLINE OF SYSTEM                  |                                                  |

| 2. SYSTEM MICROPROCESSOR              | SECTION VI                                       |

| BLOCK 3-4                             |                                                  |

| 3. MICROPROCESSOR RESETTING           | <b>RGB CIRCUIT 6-1</b>                           |

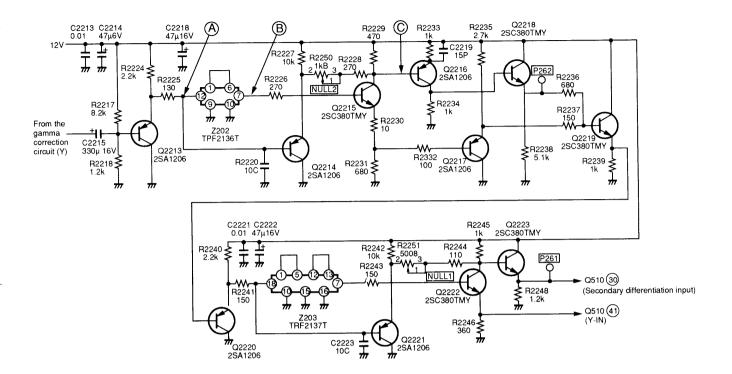

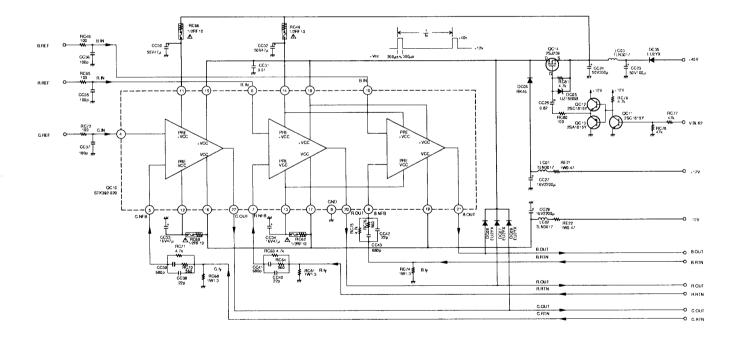

| BLOCK 3-6                             | 1. OUTLINE 6-2                                   |

| 4. REMOTE CONTROL RECEPTION BLOCK 3-7 | 2. INPUT SIGNAL SWITCHING CIRCUIT 6-2            |

|                                       |                                                  |

| 5. RS-232C TRANSMITTER/               | 3. VIDEO SIGNAL AMPLIFIER CIRCUIT 6-2            |

| <b>RECEIVER BLOCK3-8</b>              |                                                  |

| 6. CONTROL MODE                       | 4. VIDEO BLANKING CIRCUIT 6-3                    |

| READING BLOCK 3-9                     | 5. ON-SCREEN SIGNAL/TEST                         |

| 7 NICONI VICONI ACCIO LO              | CICNAL BROCEGG CIRCUIT (2)                       |

| 7. NON-VOLATILE                       | SIGNAL PROCESS CIRCUIT 6-3                       |

| MEMORY BLOCK 3-10                     | 6. BRIGHTNESS CONTROL                            |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT 6-3                |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| MEMORY BLOCK                          | <ul> <li>6. BRIGHTNESS CONTROL CIRCUIT</li></ul> |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| MEMORY BLOCK                          | 6. BRIGHTNESS CONTROL CIRCUIT                    |

| SE            | CCTION VIII                                          | SECTION XI                                        |

|---------------|------------------------------------------------------|---------------------------------------------------|

| DF            | EF CIRCUIT 8-1                                       | CONVERGENCE OUTPUT                                |

| 1.            | OUTLINE 8-2                                          | CIRCUIT (FOCUS/                                   |

| 2.            | VERTICAL F/V CONVERSION                              | CONV-OUT PC BOARD)11-1                            |

| _             | CIRCUIT 8-2                                          |                                                   |

| 3.            | VERTICAL PHASE CIRCUIT 8-3                           | 1. OUTLINE11-2<br>2. DESCRIPTION OF OPERATION11-2 |

| 4.            | VERTICAL OSCILLATION CIRCUIT8-5                      | 2. DESCRIPTION OF OFERATION11-2                   |

| 5.            | VERTICAL SAW-TOOTH WAVE-                             | SECTION XII                                       |

|               | FORM GENERATION CIRCUIT 8-6                          | HIGH VOLTAGE                                      |

| 6.            | VERTICAL REFERENCE WAVE-                             |                                                   |

| ~             | FORM GENERATION CIRCUIT 8-7                          | CIRCUIT 12-1                                      |

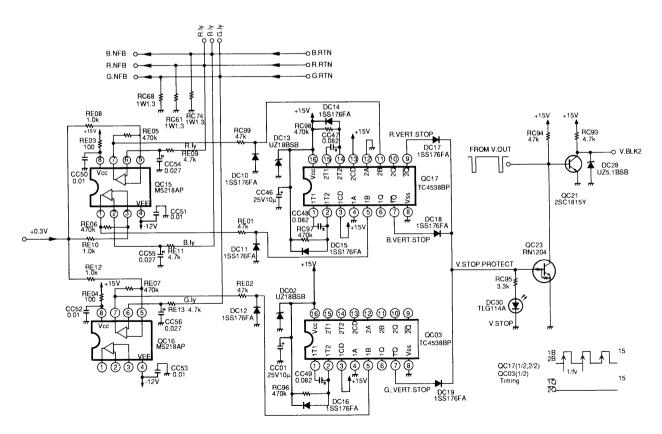

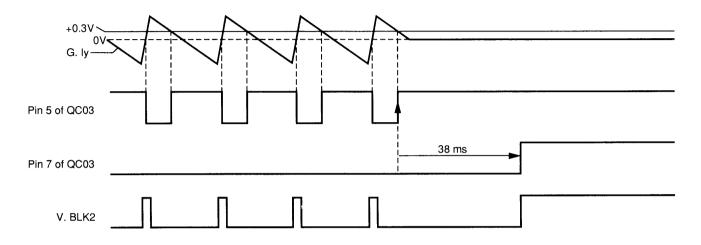

| 7.<br>8.      | VERTICAL OUTPUT CIRCUIT 8-9 VERTICAL DEFLECTION STOP | 1. HIGH VOLTAGE OSCILLATION CIRCUIT 12-2          |

| 0.            | PROTECTION CIRCUIT 8-10                              | 2. OUTPUT CIRCUIT 12-2                            |

| 9.            | VERTICAL BLANKING CIRCUIT8-11                        | 3. HIGH VOLTAGE                                   |

| - •           | OUTLINE OF HORIZONTAL                                | CONTROL CIRCUIT 12-2                              |

| 10.           | CIRCUIT8-11                                          | 4. X-RAY PROTECTION CIRCUIT 12-2                  |

| 11.           | HORIZONTAL OSCILLATION                               | 5. HV STOP CIRCUIT 12-3                           |

|               | SYNC CIRCUIT 8-12                                    | 6. SCREEN VOLTAGE                                 |

| 12.           | CONSTANT SWITCHING OF                                | GENERATION CIRCUIT 12-3                           |

|               | LOW FREQUENCY BAND AND                               | 7. ABL VOLTAGE                                    |

|               | HIGH FREQUENCY BAND 8-12                             | GENERATION CIRCUIT 12-3                           |

|               | H. STOP CIRCUIT 8-13                                 | 8. HIGH VOLTAGE                                   |

| 14.           | CONTROL VOLTAGE OF                                   | LIMITATION CIRCUIT 12-4                           |

|               | HORIZONTAL OSCILLATION                               |                                                   |

| 1.5           | FREQUENCY 8-13 HORIZONTAL DRIVE PULSE                | SECTION XIII                                      |

| 15.           | DUTY CONTROL VOLTAGE 8-13                            | H-OUT CIRCUIT 13-1                                |

| 16.           | HORIZONTAL PHASE                                     | 1. HORIZONTAL SIZE CIRCUIT 13-2                   |

|               | ADJUSTMENT CIRCUIT 8-15                              | 2. KEYSTONE AND                                   |

| 17.           | HORIZONTAL F/V                                       | PINCUSHION DISTORTION                             |

|               | CONVERSION CIRCUIT 8-15                              | CORRECTION CIRCUIT 13-3                           |

|               |                                                      | 3. H. STOP CIRCUIT 13-3                           |

| SF            | ECTION IX                                            | 4. DRIVE CIRCUIT 13-4                             |

| H             | ORIZONTAL FOCUS                                      | 5. CENTERING                                      |

|               | UTPUT CIRCUIT 9-1                                    | ADJUSTMENT CIRCUIT 13-4                           |

|               |                                                      | 6. LINEARITY ADJUSTMENT CIRCUIT 13-4              |

| 1.            | OUTLINE 9-2 DESCRIPTION OF OPERATION 9-2             | 7. R, G AND B AMPLITUDE                           |

| 2.            | DESCRIPTION OF OPERATION 9-2                         | VARIATION ADJUSTMENT 13-4                         |

| CI            | ECTION X                                             | 8. BLANKING PULSE                                 |

|               |                                                      | GENERATION CIRCUIT 13-5                           |

| C             | ONVERGENCE CIRCUIT                                   | 9. PROTECTION CIRCUIT 13-5                        |

| $(\mathbf{C}$ | CONV/FOCUS                                           |                                                   |

| P             | C BOARD) 10-1                                        |                                                   |

| 1.            |                                                      |                                                   |

| 2.            | DESCRIPTION OF                                       |                                                   |

|               | CIRCUIT OPERATION 10-2                               |                                                   |

### SECTION I OPTICAL SYSTEM

#### 1. NECK COMPONENTS

### 1-1. Parts Components Around the Neck of Projection Cathode Ray Tube

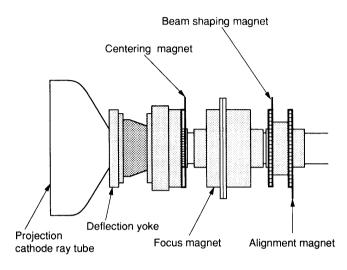

Fig. 1-1 shows the parts components around the neck of projection cathode ray tube.

Fig. 1-1 Parts components around the neck of projection cathode ray tube

#### 1-2. Description of Operation

As the components around the neck, there are provided the deflection yoke (which consisted of the main yoke, sub-yoke and centering magnet), focus magnet, beam shaping magnet and alignment magnet (the beam shaping magnet and the alignment magnet are united).

The main yoke of deflection yoke is composed of horizontal and vertical deflection coils, and bends the light beam to the horizontal and vertical directions. The sub-yoke is also called a convergence yoke, which is composed of horizontal and vertical coils, and functions to adjust the distortion by the adjustment current supplied from the convergence output circuit and to overlap the red, green and blue colors on the screen. The centering magnet is composed of bipolar magnet, located at the rear of deflection yoke and is for adjusting the picture position.

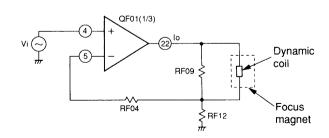

The focus magnet is composed of the permanent magnet and the coil, and makes the center and periphery of screen to be the uniform focus image by flowing to the coil the current of parabolic waveshape supplied from the focus circuit.

The beam shaping magnet and the alignment magnet are composed of tetra polar and bipolar magnets respectively, and are used for enhancing the focus quality similarly to the focus magnet.

### 2. FUNCTIONS OF MAJOR COMPONENTS

#### 2-1. Outline

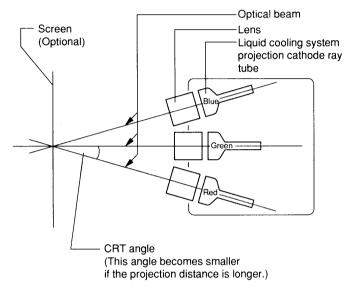

The optical system of P7300U is composed of the projection cathode ray tube and the lens as shown in Fig. 1-2. The screen is an optional parts. This unit can not only applied to the front projection system screen but also to the rear projection system screen.

Fig. 1-2 Optical system components of P7300U

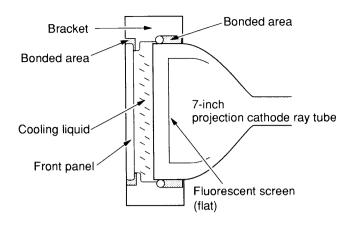

#### 2-2. Air Coupling and Liquid Cooling System Projection Cathode Ray Tube

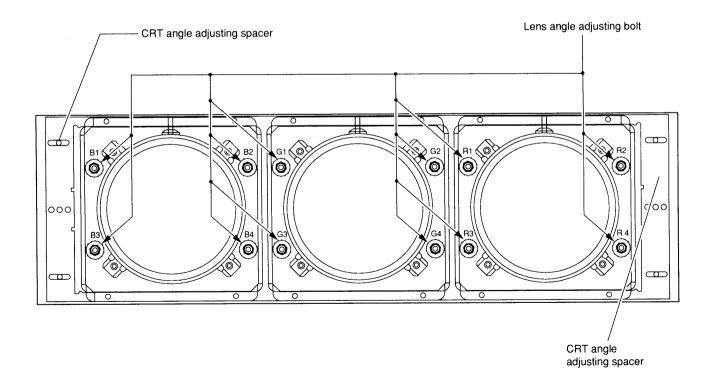

The projection cathode ray tube of this unit applies the liquid cooling system projection cathode ray tube which has the cooling function to the projection cathode ray tube itself as shown in Fig. 1-3. Apart from the projection cathode ray tube for optical coupling where the cooling liquid is sealed between the projection cathode ray tube and lens, this has no fear of cooling liquid leakage when replacing the projection cathode ray tube. In addition, the CRT angle and the lens angle meeting the projection distance and screen incidence angle can be set without replacing the lens holder as conventionally needed.

The CRT angle is the light beam angles of red and blue against that of green, and this angle needs to be made smaller as longer becomes the projection distance. The CRT angle of this unit employs 3-stage adjustable mechanism system and can be applied to this unit with its screen size from 70 to 300 inches.

Fig. 1-3 Air coupling and liquid cooling system projection cathode ray tube

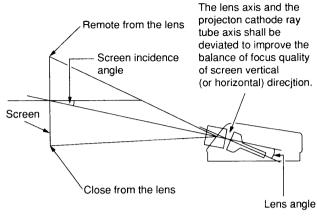

When the light beam does not enter on the screen vertically as shown in Fig. 1-4, the difference in the distance from the lens (projection cathode ray tube) in the screen vertical (horizontal) direction is brought forth. This cuases the imbalance of the focus quality in vertical (or horizontal) direction of the screen.

To correct the imbalance, the lens angle is provided between the lens axis and the projection cathode ray tube.

Fig. 1-4 Lens angle

The setting of CRT angle and lens angle can be adjusted by the mechanism shown in Fig. 1-5 according to the unit installation conditions. For the detailed adjustment method, refer to the installation manual.

Fig. 1-5 Adjustment mechanism of CRT angle and lens angle

#### 2-3. Lens

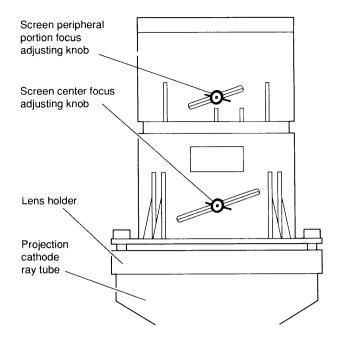

The lens forms the image on the face plate of projection cathode ray tube on the screen. The lens used in this set are provided with the adjusting nut (projection cathode ray tube side) to improve the focus quality at the screen center (entirety) and that to only improve the focus quality at the peripheral portion of the screen as shown in Fig. 1-6. First, the focus at the screen center is adjusted and then the focus at the periphery of screen is adjusted.

Moreover, the lenses for green and red are provided with the color filters for respective colors and function to enhance the purity of respective colors.

Fig. 1-6 Lens

### SECTION II POWER SUPPLY CIRCUIT

#### 1. OUTLINE

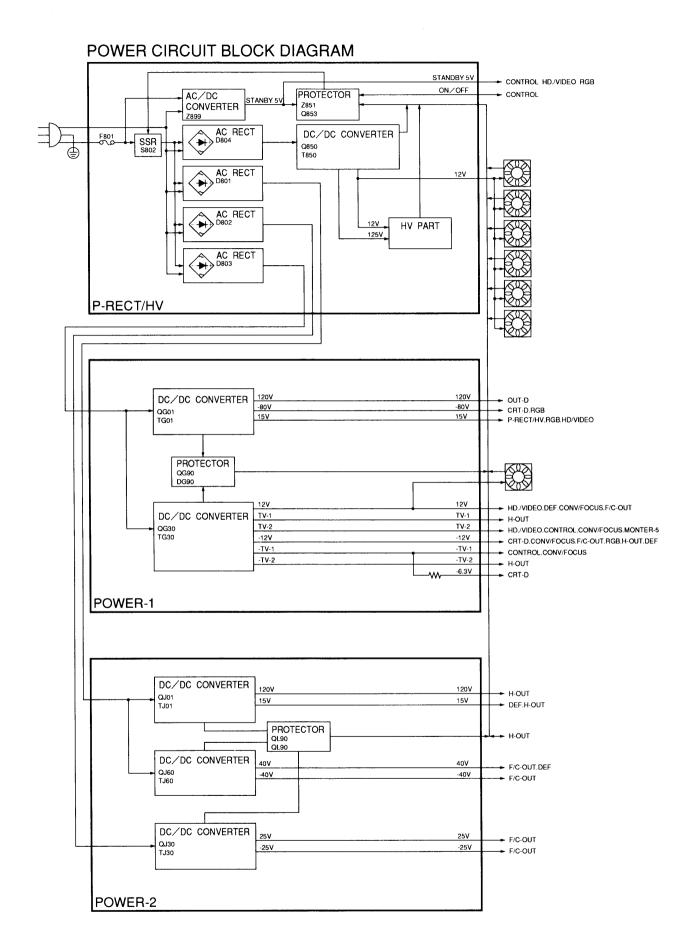

The block diagram of power supply circuit of this set is shown in Fig. 2-2.

The power supply circuit is composed of 3 PC boards of P-RECT/HV, POWER-1 and POWER-2.

The P-RECT/HV PC board is mainly composed of the stand-by power supply, AC rectifier circuit, the power supply for high voltage circuit, the protection circuit to stop the set in an emergency case and a part of high voltage circuit.

POWER-1 is mainly composed of 2 DC/DC converters. POWER-2 is mainly composed of 3 DC/DC converters.

#### 2. P-RECT/HV PC BOARD

With the main power supply turned on, the AC power supply is supplied to the AC/DC converter (Z899) outputting the stand-by 5V. The converter inputs the commercially available power supply to obtain the insulated 5V, and is of module type. The output is supplied to the microprocessor controlling the system control of the set, and also supplied to the interface circuit for inputting and outputting the remote control input circuit and external control signal. The output is supplied to the CONTROL PC board (microprocessor, etc.), HD/VIDEO PC board (interface circuit, wired remote control input circuit) and RGB PC board (remote control light receptacle).

When the power supply of the set is turned ON using the remote control or external control terminal, the ON/OFF output terminal of microprocessor develops Hi. The terminal signal is supplied to pin 2 of P851 of this PC board via the resistor, and Q853 is turned on.

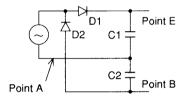

With Q853 turned on, the current flows into the control circuit of SSR (solid state relay, S802) with the standby 5V as its power supply, connects the AC side circuit and supplies the power supply to the rectifier circuit in the next stage. The AC rectifier circuit performs the double voltage rectification. The operation is explained hereunder.

When the positive half cycle is input with A-point as its reference, the current not only flows to the AC line via D1 and C1 but also charges the C1 and develops the voltage of the peak value. The peak value is the root twice of input voltage (effective value).

Further, the negative half cycle current not only flows into the AC line via C2 and D2 but also charges C2. The voltage becomes the value of peak value with the B-point being negative if viewed with A-point as a reference.

Because the output voltage between B-point and E-point equals to the total of voltages charged to C1 and C2, it becomes twice the input voltage and moreover the root twice.

The rectifier circuit is composed of 4 circuits of D801 to D804. The rectification output of D803 is supplied to POWER-1, the rectification outputs of D801 and D802 are supplied to POWER-2 and become the input of DC/DC converter in the next stage. The rectification output of D804 is supplied to the DC/DC converter (composed of Q850, etc.) supplying the power of high voltage circuit inside this PC board.

The operation principle of DC/DC converter is explained hereunder. (The projector uses 6 DC/DC converters except for the standby power supply. The operation principle is quite the same).

Fig. 2-1

Fig. 2-2 Power supply block diagram

The converter system is the switching power supply of the fly-back system, and the element used is STR-S6709. This IC has the following functions.

Table 2-1

| Pin No. | Function                                                                       |  |

|---------|--------------------------------------------------------------------------------|--|

| 1       | Collector of switching transistor.                                             |  |

| 2       | Emitter of the switching transistor and ground for HIC.                        |  |

| 3       | Base of switching transistor.                                                  |  |

| 4       | Pulling the base accumulated charge when turning off the switching transistor. |  |

| 5       | Supplying the base current to turn on the switching transistor.                |  |

| 6       | Input to detect the over-current of switching transistor.                      |  |

| 7       | Feedback terminal to keep the output voltage to be constant.                   |  |

| 8       | Input to stop the switching.                                                   |  |

| 9       | Power supply for HIC.                                                          |  |

#### 2-1. Start-up Operation

When the input (primary rectification voltage) is applied to the converter, the capacitor C854 is charged via the starting resistances R862 and R866. The voltage at both ends of capacitor gradually goes up as the charging time passes. and the voltage of pin 9 of hybrid IC Q850 connected to C854 goes up in the same way. Pin 9 of Q854 is used as the power supply pin, and when the voltage of pin 9 becomes higher than approx. 8V, Q850 starts its operation (the voltage stopping the operation after the start-up is lower than approx. 4.9V). When Q850 starts its operation, the switching transistor inside the HIC is turned on, and the power is supplied and stored in the converter transistor T850. When the switching transistor is turned off, the stored power is rectified by the diode of D856, and supplied to pin 9 of Q850 as the power supply for HIC via the series regulator Q851.

Then, the switching transistor is switched on and off again. When the secondary output voltage and the power supply voltage for HIC gradually go up and reach the specified value during this process, they are stabilized by the operation of feedback circuit.

Pin 9 of HIC also has the input function of over-voltage protection, and when the voltage of pin 9 has exceeded 10V, the operation is stopped and the stop state is latched with the current from the start-up resistance. This can be released by shutting off the input (or turning off the set) of converter.

The over-voltage protection using pin 9 of the converter operates when the power supply output voltage (cathode voltage of D856) for HIC becomes higher than approx. 35V.

The voltage is the total of the continuity voltages of D869 and D870 and the over-voltage operating point 10V of pin 9. If the over-voltage protection function of pin 9 is operated during a trouble, any of D869 and D870 gets shorted, so this should be kept in mind when performing the repair work.

#### 2-2. Usual Operation

When the switching transistor is turned on after the completion of start-up operation, the current flows into the primary winding of converter transistor T850, and the power is stored to the converter transformer as the magnetic flux. (At that time, the diodes D860, D861 and D856 become inverted bias and are cut off). When the switching transistor is turned off, each output winding becomes the voltage in the direction with the positive bias applied to the diode, and hence D860, D861 and D856 are turned on, rectified, charge the smoothing capacitor, obtain the constant voltage and further supply the power to the load. The output voltage on the secondary side is stabilized by controlling the ON time of the switching transistor. The converter detects 125V of secondary output line and feeds it back to Q850 of primary HIC.

When the pin 7 of HIC, Q850 is the input pin for feedback and the primary supply power increases, the current input to pin 7 is lessened and the ON time of switching transistor is elongated by the control circuit inside the HIC and thus a constant voltage can be supplied.

### 2-3. Error Amplifier and Protection Circuit (on the HIC1016 Z851)

The HIC1016 is used as the error amplifier, the protection circuit, and the output element of the entire set protection circuit.

The feedback voltage is input to pin 1 of Z851, compared with the internal reference voltage and output to pin 3. The output of pin 3 is input to the current amplifier Q852, and connected to the primary circuit via the photo coupler Q856.

The over-voltage protection of 125V line similarly divides the voltage input to pin 1 of Q851 with the resistor inside Z851, triggers the internal SCR (thyristor) when the voltage exceeded the threshold level, and turns on the internal transistor (the emitter is at the ground potential) outputting with the open collector from pin 16. Because the standby 5V is supplied to the SCR, the transistor of open collector continues to be open until the main power supply of set is switched off, and the output of pin 16 becomes the ground potential. Further, the over-voltage protection of 125V operates at the level higher than approx. 141V.

The over-current protection of 125V line inputs the both end voltage of resistor R863 to pin 1 and pin 2 of Z851, and when the voltage is higher than approx. 0.7V, the protection triggers the above mentioned SCR, and makes the pin 16 of Z851 to be the ground potential similarly to the above mentioned case. The gate pin of above mentioned SCR is connected to pin 14 of Z851, and the protection function works and turns off the set by applying the voltage to the pin during another abnormal mode. The overvoltage protection of 12V line of DC/DC converter consisting of Q850 connects to pin 14 of Q851 via the Zener diode of D864 or the diode D865 for OR circuit and the protection function works when the 12V line voltage becomes higher than approx. 22V. The mode, etc. where the protection function works will be explained separately. When the protection circuit works and the potential of pin 16 of Z851 becomes the ground, Q853 is turned off and the SSR is turned off. As described before, the main power supply switch of set needs to be turned off for releasing this.

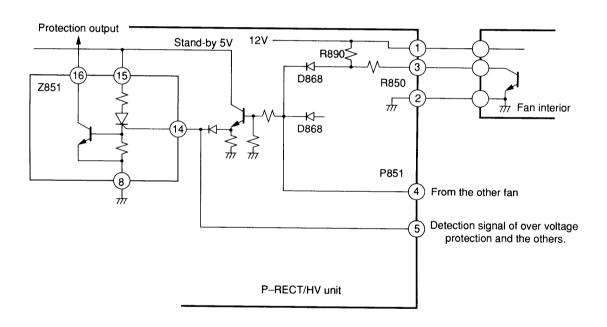

#### 2-4. Fan Stop Protection Circuit

This set uses many cooling fans. For preventing the heating when any of the fans should stop, the stop of fan actuates the protection circuit and switches off the set. A rotation stop sensor is built-in inside the used fan, and the impedance of sensor output terminal becomes greater when the fan stops. (The sensor output terminal of fan outputs with the open collector (the emitter is at the ground potential), its transistor is turned on during the rotation and turned off during the stop). This set uses many fans, but the operation is identical in all the fans, so the operation is to be explained with reference to the fan connected to P850. Pin 1 of P850 is the power supply for fan, and supplies 12V.

The stop sensor of fan is input to pin 3 of P850, and connects to the R890 as the load resistance of open collector transistor inside the fan. Since the transistor inside the fan is turned on during the usual rotation, pin 3 of P850 becomes almost the ground potential. Because the transistor is turned off during the stop, the potential of pin 3 goes up to approx. 8V which is the potential where the power supply voltage 12V is divided with the R890, R885 and R891, and the base of transistor Q854 becomes almost 4V via the diode D868.

Further, the signal is supplied to pin 14 of HIC Z851 for protection via the emitter follower of Q854 and switches off the set. When any of many fan stop signals should be stopped in the OR circuit of D868, the set is securely turned off.

Fig. 2-3

#### 3. POWER-1 PC BOARD

The POWER-1 PC board uses as its input the AC rectification output from the above mentioned P-RECT/HV PC board, forms the necessary secondary voltage with two DC/DC converters and supplies it to the load.

The DC/DC converter composed of QG01, etc. supplies the power supply to the video circuit. The output voltages are 3 kinds of 120V, –80V, and 15V.

The DC/DC converter composed of QG30, etc. forms the  $\pm 12V$  and  $\pm 7V$  and supplies them to each circuit. The  $\pm 7V$  uses 2 systems each of rectification circuit because the supplied current is much, and is supplied to the load as 7V-1 and 7V-2 and -7V-1 and -7V-2.

The over-voltage protection circuit is in the positive output line, and works when the threshold voltages of Zener diodes are exceeded respectively. During the over-voltage, the voltage is applied to the SCR and the gate of DG90 via DG20, DG18, DG49, DG50 and DG51 for OR circuit from the Zener diode. When the SCR is turned on, the luminous diode DG91 illuminates, and moreover the transistor QG90 is turned on and the collector develops approximately 5V of the power supply voltage. The collector of QG90 is connected to pin 14 terminal of HIC1016 via the diode DG92 for OR circuit and the connector P851 pin 5 of P-PECT/HV PC board. Therefore, the set is turned off when QG 90 is turned on. Further, since the power supply of SCR uses the standby 5V, the luminous diode is lighted up until the main power supply of set is switched off.

#### 4. POWER-2 PC BOARD

The POWER-2 PC board forms the necessary secondary voltage with 3 DC/DC converters and supplies it to the load with the AC rectifying output from the above mentioned P-RECT/HV PC board as its input.

The DC/DC converter composed of QJ01, etc. supplies the power mainly to the horizontal deflection circuit. The voltages output are 2 kinds of 120V and 15V.

The DC/DC converter composed of QJ60, etc. supplies the power to the output circuit of horizontal dynamic focus. The voltages output are 2 kinds of ±40V.

The DC/DC converter composed of QJ30, etc. supplies the power to the convergence output circuit. The voltages output are 2 kinds of ±25V.

The over-voltage protective circuit is in the positive output line, and designed to work when the threshold voltages of Zener diodes are exceeded respectively. The operation is similar to the above mentioned POWER-1.

#### 5. PROTECTION CIRCUIT

This circuit has a function to switch off the set during an abnormality. The mode for its function operated is shown in table 2-2.

There are abnormality detecting circuits of mentioned items 1 through 15 in table 2-2. Since any of the detection circuit operations switches off the SSR (Solid State Relay (S802 inside the P-RECT/HV PC board)) of set, the set stops its operation. Its state is maintained while the standby 5V is supplied. For releasing it, the AC input power supply must be switched off to stop the supply of standby 5V.

Table 2-2

| No. | Detection mode        | PC board  | Detection line                              | Operation confir-<br>mation point     | Remarks                                           |

|-----|-----------------------|-----------|---------------------------------------------|---------------------------------------|---------------------------------------------------|

| 1   | Over voltage          | P-RECT/HV | 125V                                        | 125V line voltage                     | Operating at the voltage higher than 134V.        |

| 2   | Over voltage          | P-RECT/HV | 12V                                         | 12V line voltage                      | Operating at the voltage higher than 22V.         |

| 3   | Over current          | P-RECT/HV | 125V                                        | Both ends voltage of R863             | Operating at the serial current higher than 1.3A. |

| 4   | Over voltage          | POWER 1   | 120V                                        | 120V line voltage                     | Operating at the voltage higher than 140V.        |

| 5   | Over voltage          | POWER 1   | 15V                                         | 15V line voltage                      | Operating at the voltage higher than 22V.         |

| 6   | Over voltage          | POWER 1   | 12V                                         | 12V line voltage                      | Operating at the voltage higher than 18V.         |

| 7   | Over voltage          | POWER 1   | 7V                                          | Voltage of LG46                       | Operating at the voltage higher than 10V.         |

| 8   | Over voltage          | POWER 1   | 7V                                          | Voltage of LG45                       | Operating at the voltage higher than 20V.         |

| 9   | Over voltage          | POWER 2   | 120V                                        | 120V line voltage                     | Operating at the voltage higher than 140V.        |

| 10  | Over voltage          | POWER 2   | 15V                                         | 15V line voltage                      | Operating at the voltage higher than 22V.         |

| 11  | Over voltage          | POWER 2   | 40V                                         | 40V line voltage                      | Operating at the voltage higher than 51V.         |

| 12  | Over voltage          | POWER 2   | 25V                                         | 25V line voltage                      | Operating at the voltage higher than 30V.         |

| 13  | Fan stops             | All fans  | Rotation stops                              | Presence or<br>absence of<br>rotation | Rotation stop sensor is built-in for all fans     |

| 14  | X-ray protection      | P-RECT/HV | High voltage control voltage                | DB18 cathode                          | Operating at the voltage higher than 20V.         |

| 15  | Horizontal sweep stop | H-OUT     | Presence or<br>absence of<br>fly-back pulse | DA13 cathode                          | Operating at the voltage higher than 7V.          |

For checking which abnormality detecting circuit is operating and the set stops, investigate the voltage in the operation confirmation point in the above table based on the value given in the remarks column. If the over-voltage protective circuit of power supply line inside the POWER-1 should operate, DG91 (LED) inside the POWER-1 comes on. This LED continues to get lighted until the main power supply of set is switched off. Similarly, if the over-voltage protective circuit of power supply line inside the POWER-2 should operate, DJ91 (LED) inside the POWER-2 comes on.

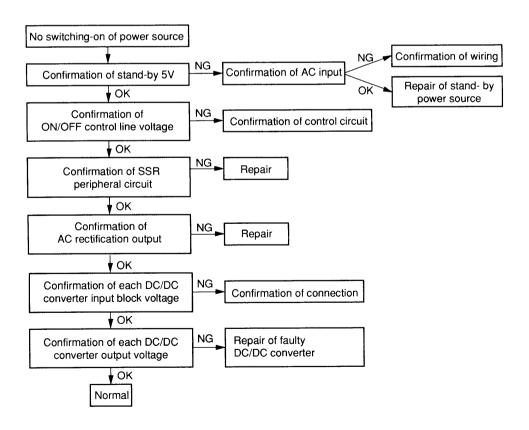

#### 6. TROUBLESHOOTING

#### 6-1. Precautions during the Repair

Because this paragraph includes the contents concerning the PL, you are requested to surely perform the work.

(1) When replacing the fuse (F801 inside the P-RECT/HV unit) of AC input block, be sure to solder the lead wire of fuse to the wiring board. (If the wire is not soldered, the fuse may radiate heat with the contact resistance of the holder and be broken.).

- (2) When mounting the P-RECT/HV unit block (the assembled block with the unit, fan, power supply switch, AC inlet and metal parts) to the main body, surely tighten the fixing screws (3 screws of 4 mm) with the chassis. (The chassis is grounded with the connection of these screws. Improper connection may cause the danger for electric shock).

- (3) The position of internal wiring and the protection parts (tube, binding band, tape, etc.) for wire materials must be returned to the previous state without fail. (The danger for electric shock due to the contact to heating parts, the contact between charged block and noncharged block and the damage to the cover may occur).

When the protection circuit operates and the set is turned off after supplying the power, check to see in which mode the protection circuit operates referring to the protection circuit section of the service data. After that, perform the followings depending on the cause for the protection circuit to operate.

- (1) Protection operation due to the over-voltage Check the applicable DC/DC converter.

- (2) Protection operation due to the over-current Check the high voltage circuit (loaded circuit).

- (3) Protection operation due to the fan stop Check the fan and its periphery circuit.

- (4) Protection operation due to the X-ray protection Check the high voltage circuit.

- (5) Protection operation due to the horizontal sweep stop Check the horizontal deflection circuit.

When the switching transistor built-in inside the HIC (STR-S6709) which is used for the DC/DC converter is short-circuited and defective, the following cases may be considered that the fuse in DC/DC converter input block may break and/or the Zener diode connected to the ground from pin 2 of HIC may be short-circuited. When the Zener diode is short-circuited, the protection circuit limiting the collector current of the switching transistor doesn't operate. In case of the trouble phenomenon as described above, check the Zener diode.

When the fuse FJ07 of 40V line of DC/DC convertor consisting of QJ40 of POWER-2, etc. breaks, the Zener diodes DJ81 and DJ82 may be short-circuited. Further, when the 25V line fuse FJ04 of DC/DC converter consisting of QJ30, etc. breaks, the Zener diodes DJ51 and DJ80 may be short-circuited. When the Zener diodes are short-circuited, the over-voltage protection of pin 9 of switching HIC operates and stops the switching function.

### SECTION III MICROPROCESSOR (CONTROL)

#### 1. OUTLINE OF SYSTEM

The system microprocessor of P7300U is developed as the program with consciousness paid to the easiness of maintenance such as the use of external program ROM, inscription of construction, realization of modular parts, realization of multi files and control by mode.

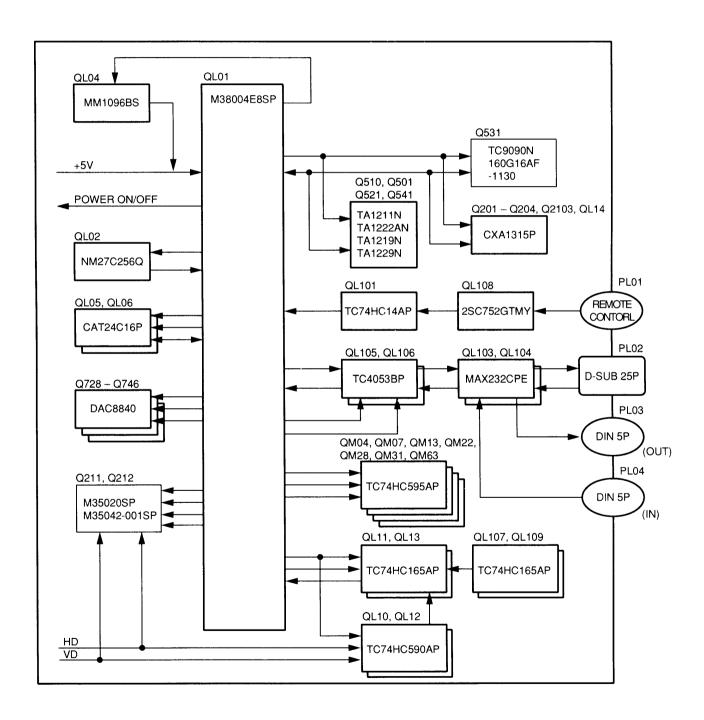

Fig. 3-1 shows the system block diagram.

Fig. 3-1 System control block diagram

The main functions of system microprocessor is described below.

· Control input relation

play processing.

- Remote control reception processing, RS-232C transmission and reception processing, RS-422 transmission and reception processing, input signal type identification process.

- System control relation

Non-volatile memory control processing, on-screen dis-

- Deflection/convergence system control relation

Deflection system control processing, centering control processing, analog convergence control processing.

- Video system control relation

Video adjustment control processing, white balance control processing, shading correction processing, color signal control processing.

The main special features in this machine model are listed below.

#### 1-1. Convergence Circuit

The convergence circuit is controlled by the analog convergence control by the S/P control DAC, the fine adjustment is available for every point similarly to the digital convergence, and adopts the picture pursuit system where the convergence hardly gets deviated even when changing the picture size.

#### 1-2. Input Signal Automatic Identification

The convergence bank and the source bank are identified by judging the vertical frequency/horizontal frequency of input signal. The convergence bank can memorize 7 modes in total of 15 to 18 kHz, 19 to 25 kHz, 26 to 33 kHz, 34 to 44 kHz, 45 to 59 kHz, 60 to 79 kHz and 80 to 100 kHz of horizontal frequency with the convergence adjustment/deflection adjustment data as its center, while the source bank can identify the difference of horizontal and vertical frequencies and memorize 30 modes such as picture size, picture phase, contrast, brightness, color, tint and sharpness data, which can judge the signal every time when the input signal changes, and automatically call out the adjustment data meeting it.

### 1-3. Adjustment Data Reading Function by Control RS-232C/RS-422

The adjustment data can be read out by controlling the RS-232C and RS-422 from the outside, and the read/write processing can be made by the dedicated software, thus facilitating a variety of adjustments.

### 2. SYSTEM MICROPROCESSOR BLOCK

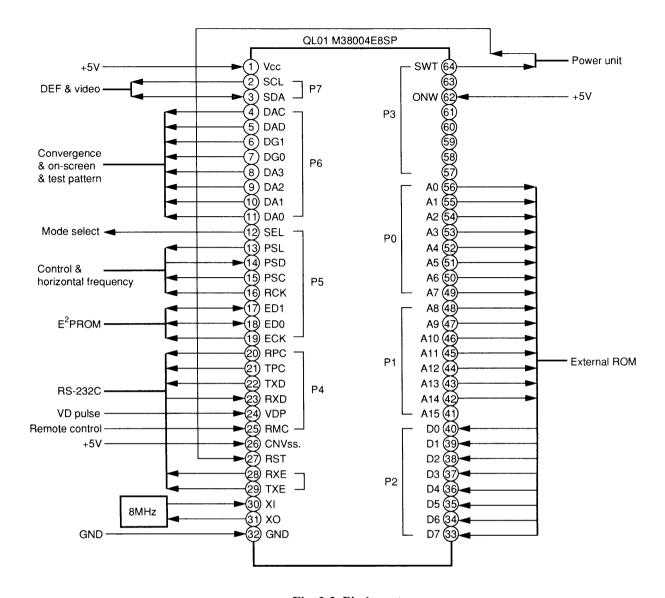

As the system microprocessor of QL01, the 8-bit microprocessor controller (M38004E8SP) is employed.

This system microprocessor doesn't use the program area existing inside, but uses the EPROM (NM27C256Q) as the program ROM outside the QL02, thereby making it easier to change the specifications of system microprocessor and to repair the bug and to maintain the machine.

Further, the system microprocessor controls all the controls such as the input system control process, deflection system control process, video system control process, display system control process, input identification process and adjustment data input/output process, etc. as shown in Fig. 3-2 and table 3-1.

**Table 3-1 Pin function**

| Pin No. | Name  | Function                                             | I/O |

|---------|-------|------------------------------------------------------|-----|

| 1       | VCC   | Power supply                                         | I   |

| 2       | SCL   | I <sup>2</sup> C bus clock for video                 | 0   |

| 3       | SDA   | I <sup>2</sup> C bus data for video                  | 1/0 |

| 4       | DAC   | Clock for DAC8840/Load 1 for on-screen               | 0   |

| 5       | DAD   | Data for DAC8840/Load 0 for on-screen                | 0   |

| 6       | DG1   | Gate 1 for DAC8840/Data for on-screen                | 0   |

| 7       | DG0   | Gate 0 for DAC8840/Clock for on-screen               | 0   |

| 8       | DA3   | Data 3 for DAC8840/Load for serial parallel          | 0   |

| 9       | DA2   | Load data 2 forDAC8840/Data for serial parallel      | 0   |

| 10      | DA1   | Load data 1 for DAC8840/Clock for serial parallel    | 0   |

| 11      | DA0   | Load data 0 for DAC8840                              | 0   |

| 12      | SEL   | DAC8840 OR on-screen, serial/parallel control select | 0   |

| 13      | PSL   | Load for parallel/serial                             | 0   |

| 14      | PSD   | Data for parallel/serial                             | 1   |

| 15      | PSC   | Clock for parallel/serial                            | 0   |

| 16      | RCK   | Load for horizontal frequency                        | 0   |

| 17      | ED1   | Data 1 for non-volatile memory                       | 1/0 |

| 18      | ED0   | Data 0 for non-volatile memory                       | I/O |

| 19      | ECK   | Clock for non-volatile memory                        | 0   |

| 20      | RPC   | Personal computer sending enable                     | 0   |

| 21      | TPC   | Personal computer reception enable                   | 0   |

| 22      | TXD   | RS-232C sending data                                 | 0   |

| 23      | RXD   | RS-232C reception data                               | I   |

| 24      | VDP   | Vertical retrace period pulse                        | ı   |

| 25      | RMC   | Remote control reception data                        | 1   |

| 26      | CNVss | Operation mode setting                               | 1   |

| 27      | RST   | External reset                                       | ı   |

| Pin No. | Name | Function                       | I/O |

|---------|------|--------------------------------|-----|

| 28      | RXE  | RS-232C reception enable       | 0   |

| 29      | TXE  | RS-232C sending enable         | 0   |

| 30      | ΧI   | Input for oscillation          | l   |

| 31      | ХО   | Output for oscillation         | 0   |

| 32      | GND  | GND                            | ı   |

| 33      | D7   | Data for external ROM (MSB)    | l   |

| 34      | D6   | Data for external ROM          | 1   |

| 35      | D5   | Data for external ROM          | 1   |

| 36      | D4   | Data for external ROM          | 1   |

| 37      | D3   | Data for external ROM          | I   |

| 38      | D2   | Data for external ROM          | 1   |

| 39      | D1   | Data for external ROM          | 1   |

| 40      | D0   | Data for external ROM (LSB)    | l   |

| 41      | A15  | Address for external ROM (MSB) | 0   |

| 42      | A14  | Address for external ROM       | 0   |

| 43      | A13  | Address for external ROM       | 0   |

| 44      | A12  | Address for external ROM       | 0   |

| 45      | A11  | Address for external ROM       | 0   |

| 46      | A10  | Address for external ROM       | 0   |

| 47      | A9   | Address for external ROM       | 0   |

| 48      | A8   | Address for external ROM       | 0   |

| 49      | A7   | Address for external ROM       | 0   |

| 50      | A6   | Address for external ROM       | 0   |

| 51      | A5   | Address for external ROM       | 0   |

| 52      | A4   | Address for external ROM       | 0   |

| 53      | A3   | Address for external ROM       | 0   |

| 54      | A2   | Address for external ROM       | 0   |

| 55      | A1   | Address for external ROM       | 0   |

| 56      | A0   | Address for external ROM (LSB) | 0   |

| 57      |      | N.C.                           | 0   |

| 58      |      | N.C.                           | 0   |

| 59      |      | N.C.                           | 0   |

| 60      |      | N.C.                           | 0   |

| 61      |      | N.C.                           | 0   |

| 62      | ONW  | External weight                | l   |

| 63      |      | N.C.                           | 0   |

| 64      | SWT  | Power supply switch            | 0   |

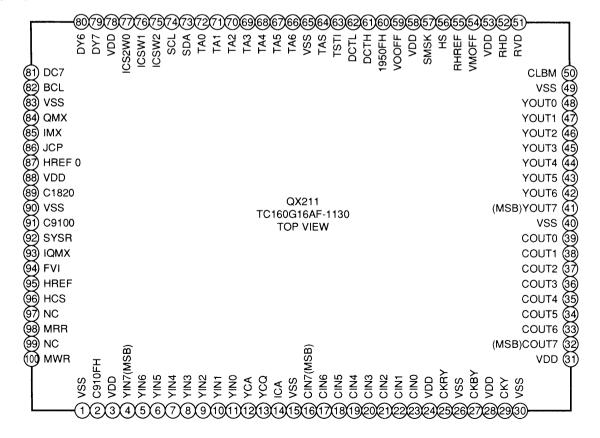

Fig. 3-2 Pin layout

#### 3. MICROPROCESSOR RESETTING BLOCK

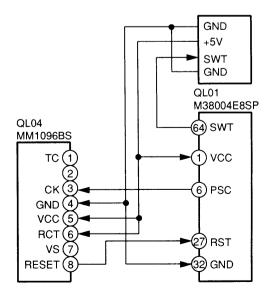

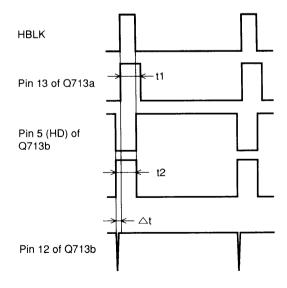

As shown in Fig. 3-3, the microprocessor resetting block adopts the watch dog timer (MM1096BS) of QL04 as the reset IC.

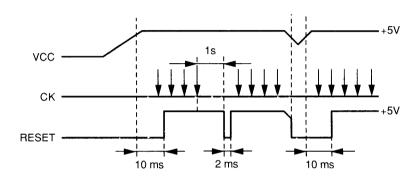

The reset IC of QL04 uses as input the clock signal for non-volatile memory described later, judges that the system microprocessor (M38004E8SP) of QL01 is running recklessly if the clock signal is absent for about 1 second, and supplies the reset signal to the system microprocessor of QL01 at the timing as shown in Fig. 3-4.

Fig. 3-3 Power source resetting block

### 4. REMOTE CONTROL RECEPTION BLOCK

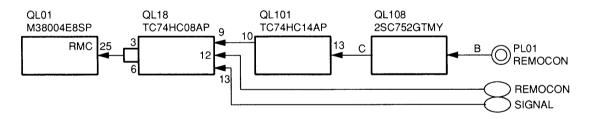

The remote control reception block converts the remote control signal of 3 V supplied from the accessory remote control unit (CT-9847) connected to the remote control terminal into the level of 5V by the transistor (2SC752GTMY) of QL108 as shown in Fig. 3-5, and after passing it through the noise removal filter, shapes the waveform by passing it through the buffer (TC74HC14AP) of QL01.

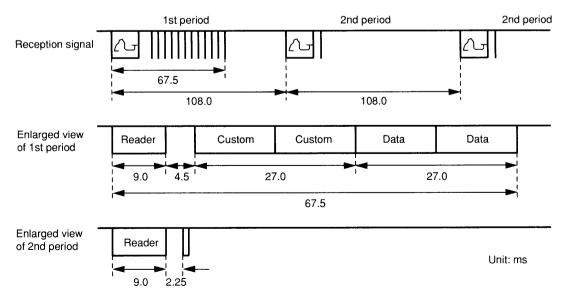

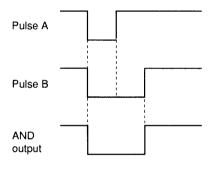

And, because the wireless remote control light reception sensors are arranged on front and rear of the unit, the signal is selected by the AND gate (TC74HC08AP) and is supplied to the system microprocessor of QL01 at the timing as shown in Fig. 3-6.

Fig. 3-4 MM1096BS reset timing diagram

Fig. 3-5 Remote control reception block

Fig. 3-6 Remote control reception signal timing diagram

#### 5. RS-232C TRANSMITTER/ RECEIVER BLOCK

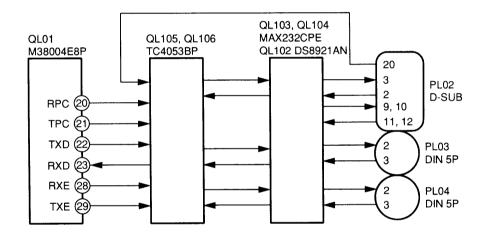

In the RS-232C transmit/receive section, as shown in Fig. 3-7, RS-232C transmit/receive signals with timings as shown in Fig. 3-8 sent from PL02 RS-232C connector (DSUB 25P), PL04 system bus input connector (DIN 5P), and PL03 system bus output connector (DIN 5P) are level-converted by the RS-232C DC/DC converter consisting of QL103, QL104. While the RS-422 transmit/receive signal is level-converted by RS-422 driver/receiver consisting of QL102 (DS8921AN). And one of them is selected in passing through analog switches (TC4053BP) of QL105 and QL106.

In this instance, they operate as the switching circuit in the transmitter/receiver of RS-232C and RS-422 according to the combination of DSR signal of pin 20 of PL02 and each signal of pin 20 (RPC), pin 21 (TPC), pin 28 (RXE) and pin 29 (TXE) of QL01.

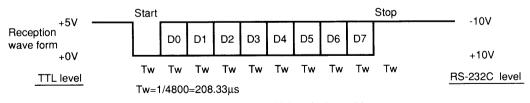

As an example of communication conditions, Fig. 3-8 is calculated upon the transmission speed of 4800 bps, no parity bit and with the bit length being 8-bit and stop bit being 1 bit.

The timing of RS-422 is identical to the above mentioned RS-232C, but the information is transmitted with the balance transmission structured of two equal signal lines.

Fig. 3-7 RS-232C/RS-422 transmitter/receiver block

Communication conditions: 4800 bps, no parity, 8-bit length, 1 stop bit

Fig. 3-8 RS-232C timing diagram

#### 6. CONTROL MODE READING BLOCK

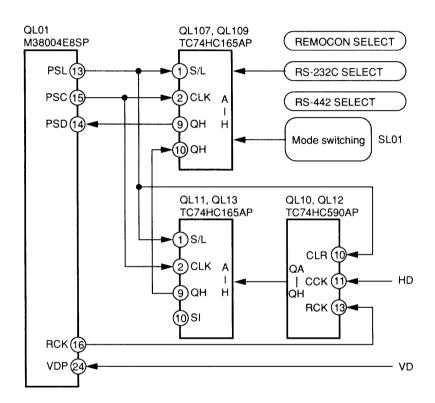

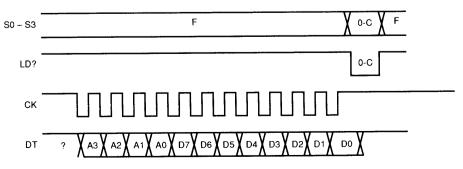

The control reading block reads two kinds of data as shown in Fig. 3-9 at the timing as shown in Fig. 3-10.

The 1st data reads the SL01 dip switch state and the mode states of wired remote control, RS-232C and RS-422 by using the P/S (TC74HC165AP) of QL107 and QL109.

The 2nd data reads the number of horizontal scanning lines for input signal identification described later by using the P/S (TC74HC165AP) of QL11 and QL13.

In the input signal type identification process, the value of counter (QL10, QL12) by the HD pulse from the outside is read out as shown in Fig. 3-9, and moreover the interruption process is conducted by the system microprocessor of QL01 and the VD pulse is discriminated by checking the time of vertical feedback period of input signal and the number of scanning lines during that period.

Thereby, 7 kinds of convergence bank signal and 30 kinds of source bank signal are identified, and the adjusted values of analog convergence and user adjustment item are controlled by mode respectively.

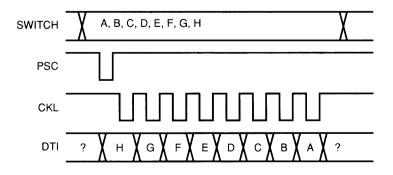

Fig. 3-9 Control mode taking block

Fig. 3-10 TC74HC165AP timing diagram

### 7. NON-VOLATILE MEMORY BLOCK

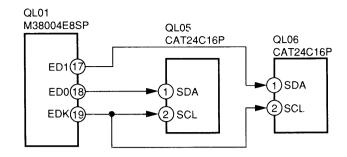

The non-volatile memory block is used for storing each of adjusting data to the nonvolatile memory (CAT24C16P) of QL05 and QL06 as shown in Fig. 3-11.

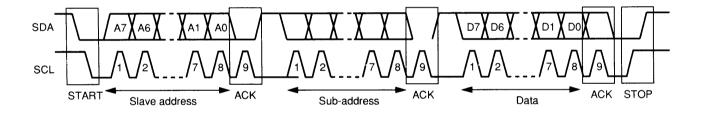

The system microprocessor of QL01 reads out and writes in all the adjusting data at the timing as shown in Fig. 3-12 when the power source is switched on (AC ON), thereby maintaining the previous state.

However, if any trouble (power source shut-off, etc.) should happen when writing the adjusting data, an error may happen to the written data, and if it is judged to be an error, the initial data which is stored into the system microprocessor of OL01 is read out and written.

Here, the adjusted value of convergence bank is stored to the non-volatile memory of QL05 and the adjusted value of source bank is stored to the non-volatile memory of QL06.

Fig. 3-11 Non-volatile memory block

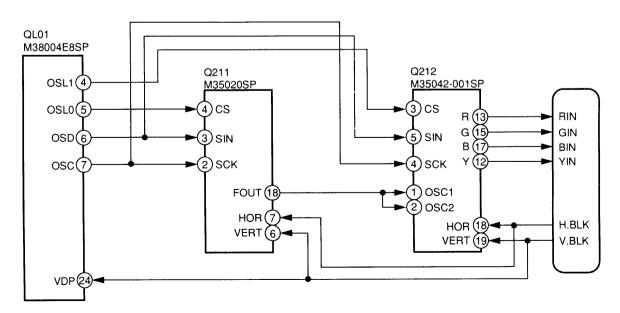

#### 8. ON-SCREEN DISPLAY BLOCK

The control signal is supplied at the timing as shown in Fig. 3-14 and Fig. 3-15 which is further shown in Fig. 3-13, and the on-screen display block generates the signal for on-screen character inscription at the timing predetermined by the self-running oscillation frequency in accordance with the VD pulse and HD pulse which are supplied separately.

Fig. 3-12 I<sup>2</sup>C bus timing diagram

Fig. 3-13 On-screen display block

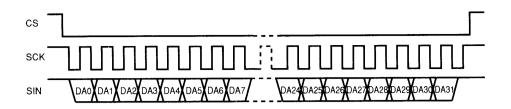

Fig. 3-14 M35020SP timing diagram

Fig. 3-15 M35042-901SP timing diagram

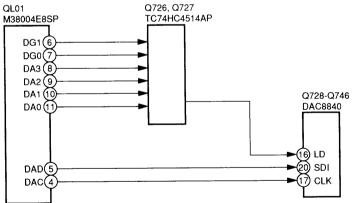

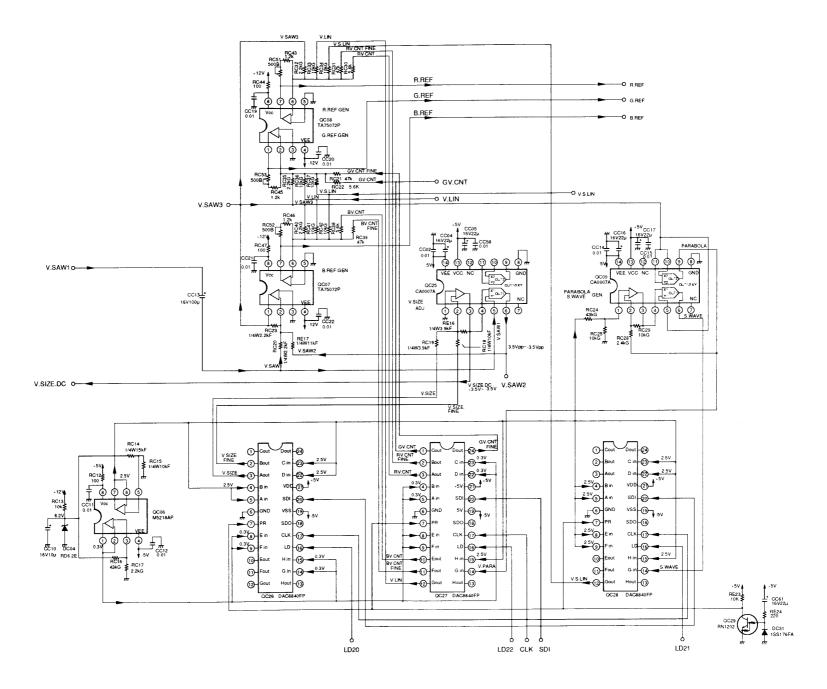

### 9. CONVERGENCE/DEFLECTION SYSTEM CONTROL BLOCK

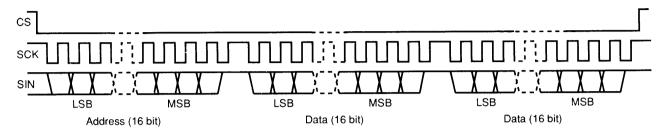

The deflection system control block performs the analog convergence/deflection system control at the timing as shown in Fig. 3-16 as illustrated in Fig. 3-17.

The load signal of gain DAC (DAC8840) is supplied for its operation by setting the data to the decoder IC (TC74HC4514AP) of Q726 and Q727 from the microprocessor of QL01.

These signals maintain the previous state in the full adjusting data reading when the power source is ON, and restores the state if the trouble such as noise should happen and the data becomes abnormal to the output signal in the refresh process (periodical data output process).

Fig. 3-16 Convergence/deflection system control block

Fig. 3-17 DAC8840 timing diagram

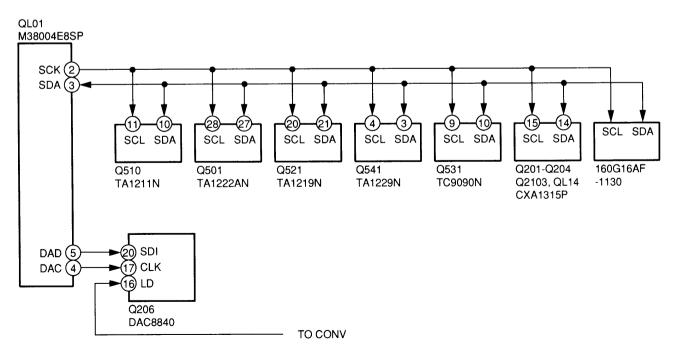

### 10. VIDEO SYSTEM CONTROL BLOCK

The video control block performs the video process, color signal process, color temperature process and moreover switching control process at the timing as shown in Fig. 3-12 and also the shading process at the timing as shown in Fig. 3-17 as illustrated in Fig. 3-18.

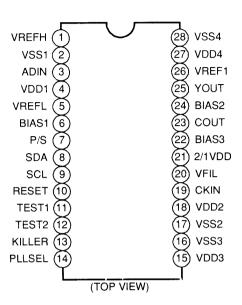

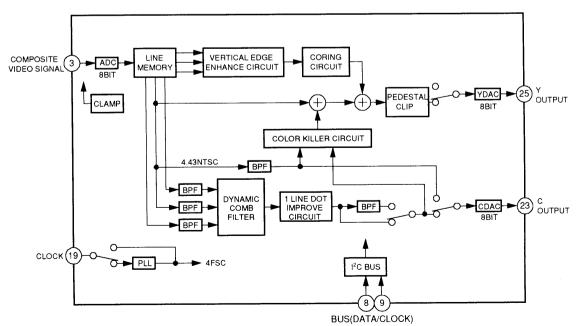

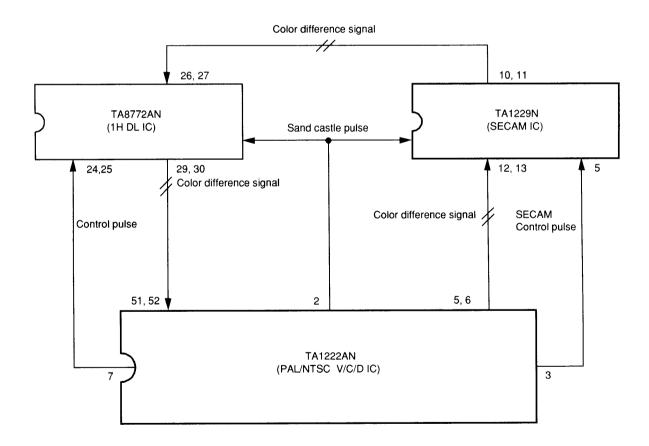

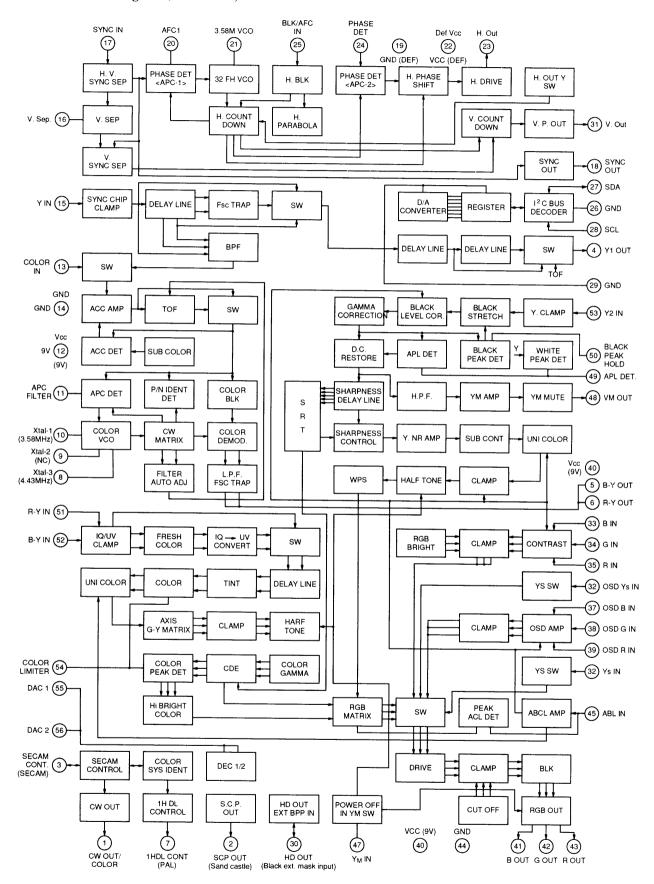

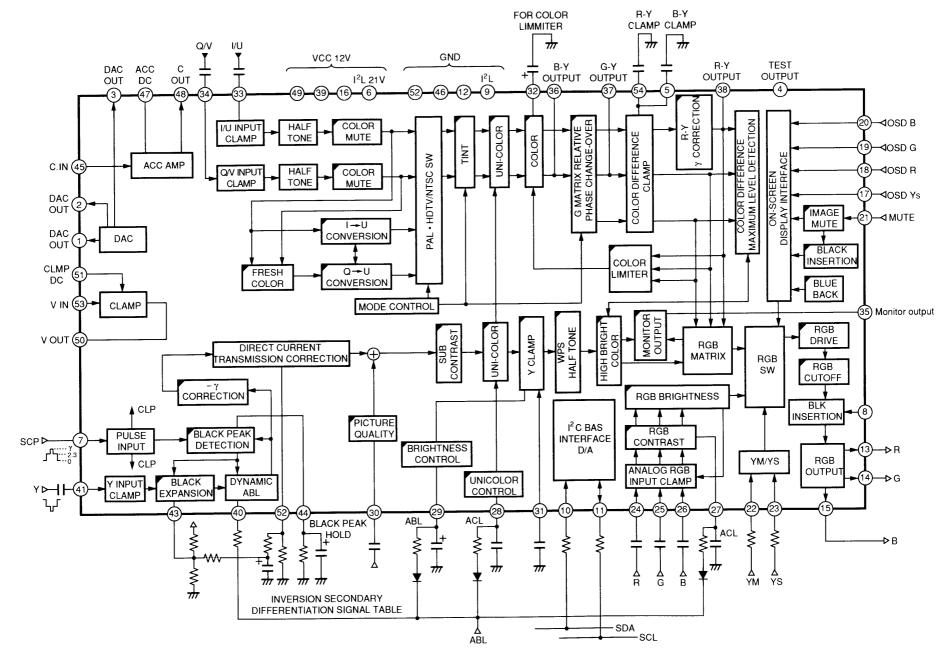

(1) Q510 (TA1211N), Q501 (TA1222AN), Q521 (TA1219), Q541 (TA1229N) and Q531 (TC9090C) of video control LSI:

The control signals for adjusting various images

- (2) The up-converter gate array (160G16AF-1130): NTSC conversion and process

- (3) I<sup>2</sup>C DAC (CXA1315P) of Q201 to Q204, Q2103 and QL14:

Contrast adjustment, brightness adjustment, color temperature adjustment, trimming adjustment and switching control

(4) Gain DAC (DAC8840) of Q206:

Control signal for correcting the shading

These signals maintain the previous state in the full adjusting data read when the power source is ON and restore the normal state when the trouble such as noise happens and the data becomes abnormal to the output signal in the refresh process (periodical data output process).

#### 11. VARIOUS CONTROL MODES

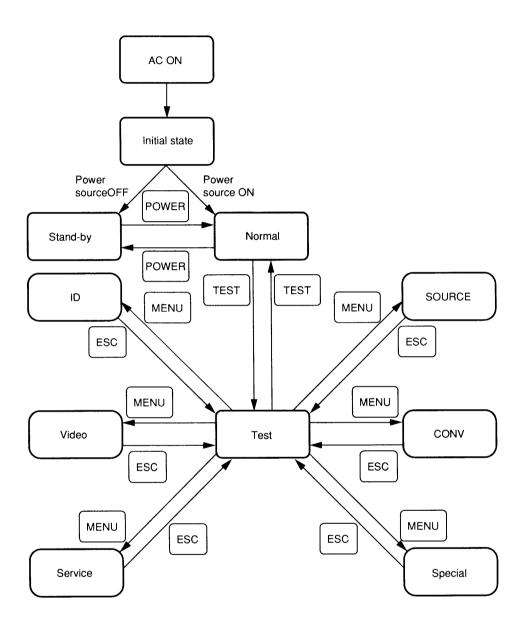

This system covers various control modes in the operation as shown in Fig. 3-19.

At first the system becomes the "initialization mode" after the AC is turned on, reads the previous adjustment data from the non-volatile memory, and sets various operation states according to that state.

The state where the sub-power source is off is called the "stand-by mode", and only the main power switch is accepted in this mode.

The state where the sub-power source is on is called the "normal mode", and the usual operation is done with this mode as its standard.

The "normal mode" of usual operation can be shifted to the "test mode" for various kinds of adjustment, while the "test mode" can be shifted to the ID controlling "ID mode", the video system controlling and setting "video mode", the unit adjusting "service mode", the state displaying "special mode, the CONV bank data setting "CONV mode" and the SOURCE bank data setting "SOURCE mode".

Fig. 3-18 Video system control block

Fig. 3-19 Various control mode transmission diagram

#### 12. RS-232C/RS-422 CONTROL METHOD

The external control method by the RS-232C/RS-422 is to be explained hereunder.

The signals shall be connected in straight system at the D-SUB25 pin connector of PL02 as shown in table 3-2 and table 3-3. This is because the signals are connected in such that they may cross inside the main body.

Table 3-2 RS-232C connection conditions

| Pin No. | Name of signal | Contents of signal      | Input/output |               | Signal from external source |

|---------|----------------|-------------------------|--------------|---------------|-----------------------------|

| 2       | RXD            | Reception data          | I            | <b>←</b>      | TXD                         |

| 3       | TXD            | Transmission data       | 0            | $\rightarrow$ | RXD                         |

| 4       | CTS            | Transmission permission | l            | <b>←</b>      | RTS                         |

| 5       | RTS            | Transmission request    | 0            | $\rightarrow$ | CTS                         |

| 6       | DTR            | Data terminal ready     | 0            | $\rightarrow$ | DSR                         |

| 7       | S.G            | Signal ground           | 1            | <b>←</b>      | S.G                         |

| 20      | DSR            | Data set ready          | i            | <b>←</b>      | DTR                         |

Table 3-3 RS-422 connection conditions

| Pin No. | Name of signal | Contents of signal | Input/output |               | Signal from external source |

|---------|----------------|--------------------|--------------|---------------|-----------------------------|

| 7       | S.G            | Signal ground      | I            | <b>←</b>      | S.G                         |

| 9       | RXD (+)        | Reception data     | I            | <b>←</b>      | RXD (+)                     |

| 10      | RXD (-)        | Reception data     | I            | <del></del>   | RXD (-)                     |

| . 11    | TXD (+)        | Transmission data  | 0            | $\rightarrow$ | TXD (+)                     |

| 12      | TXD(-)         | Transmission data  | 0            | $\rightarrow$ | TXD(-)                      |

| 13      | SEL            | RS-422 select      | ı            | <b>←</b>      | S.G                         |

The communication conditions should be set as shown in table 3-4.

Table 3-4 RS-232C/RS-422 communication conditions

|                                                                                                    | Condition                                                                                                                                                                                                                                                                                         |  |  |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System Transmission speed - 4800, Parity bit - Non, Data length - 8 bits, Stop Communication style |                                                                                                                                                                                                                                                                                                   |  |  |

| Format                                                                                             | 1 block should be composed of STX (1 byte) + ID (2 bytes) + CMD (3 bytes) + ETX (1 byte). Here, the STX is 02h, the ETX is 03h, the ID is alpha numerical letter (0 to F) + aster isk (*) and the CMD is the RS-232C/RS-422 command letter line (capital letter) shown in Table 3-5 – Table 3-12. |  |  |

The ID is the individual identification numbers when multiple projectors are connected, makes it possible to control them at the same time and usually is set to "01". If the ID number has not been set, no RS-232C command can be accepted.

The ID type basically adopts 2 bytes (0 to F) in hexadecimal digit and can be set to 256 types from "00" to "FF". Further by using the asterisk (\*) when controlling the set, the multiple sets can be controlled simultaneously instead of all the hexadecimal characters. However, the asterisk (\*) can not be used when setting the identification of projector.

As the care when sending the command, at least the time interval of around 100 ms must be provided when sending the commands. If the interval should be too short, the set doesn't work due to the erroneous recognition of command.

Especially when sending more than 3 commands continuously in the item which requires a long process time such as the power source ON/OFF and input switching, the time interval from 3 to 7 seconds must be provided on and after the 3rd command.

To the contrary, in case of the time interval of more than 1 minute, the commands which have thus far been recognized become invalid.

### 13. TABLE OF CONTROL ITEM BY EACH CONTROL MODE

The table of control items that can be operated for each control mode is listed in the table of control items of table 3-5. This table lists up the operation operable mode for every item, remote control code and RS-232C/RS-422 command.

Some commands of common mode don't work depending on the selected item.

Table 3-5

| Item             | Contents in normal mode                         |     | RS-232C/R | S-422 CMD     |     |

|------------------|-------------------------------------------------|-----|-----------|---------------|-----|

| Power ON/OFF     | Power ON/OFF                                    | PWR | PON       | POF           |     |

| VIDEO            | Video input selection                           | VNA |           |               |     |

| Y/C              | Y/C input selection                             | VNB |           |               |     |

| S-VIDEO          | S-VIDEO input selection                         | VNC |           |               |     |

| RGB1             | RGB1 input selection                            | VND |           |               |     |

| RGB2             | RGB2 input selection                            | VNE |           |               |     |

| YPbPr            | YPbPr input selection                           | PBR | РВО       | PBF           |     |

| MUTE ON/OFF      | Video mute                                      | MSW | MON       | MOF           |     |

| MENU             | Display mode switching                          | MNU |           |               |     |

| PICTURE MENU     | Video system adjustment                         | PMU |           |               |     |

| PICTURE REST     | Video system adjusting reset                    | PRS |           |               |     |

| CENTERING        | Centering adjustment                            | CEN | CER       | CEG           | CEB |

| SHIFT            | Horizontal/vertical picture position adjustment | SFT |           |               |     |

| SIZE             | Horizontal/vertical picture size adjustment     | SIZ |           |               |     |

| SOURCE MODE 1-30 | SOURCE mode                                     | SMA | S01       | $\rightarrow$ | S30 |

| TEST MODE        | Test mode switching                             | AJY |           |               |     |

| ID SET           | ID setting                                      | IDS |           |               |     |

Table 3-6

| Item          | Contents in test mode                           | RS-232C/RS-422 CMD |

|---------------|-------------------------------------------------|--------------------|

| TEST PATTERN  | Test pattern switching                          | TST                |

| SHIFT         | Horizontal/Vertical picture position adjustment | SFT                |

| SIZE          | Horizontal/Vertical picture size adjustment     | SIZ                |

| CONV MODE     | Convergence adjusting mode                      | CNV                |

| CONV SIZE     | Convergence size adjustment                     | CSZ                |

| LIN           | Linearity adjustment                            | LIN                |

| TILT          | TILT adjustment                                 | TIL                |

| BOW           | BOW adjustment                                  | BOW                |

| KEY           | KEY adjustment                                  | KEY                |

| PIN           | PIN adjustment                                  | PIN                |

| FOCUS         | Focus adjustment                                | FCS                |

| WHITE BALANCE | White balance adjustment                        | WHT                |

| TRIMMING ADJ  | Trimming adjustment                             | TRM                |

| MENU          | Display mode switching                          | MNU                |

| NORMAL MODE   | Test mode releasing                             | AJN                |

Table 3-7

| Item    | Contents in ID mode | RS-232C/RS-422 CMD |

|---------|---------------------|--------------------|

| ID. CLR | ID erasing          | IDC                |

| ID. SET | ID setting          | IDS                |

| ID. ALL | * input             | IDA                |

| 0       | 0 input             | VNO                |

| 1       | 1 input             | VN1                |

| 2       | 2 input             | VN2                |

| 3       | 3 input             | VN3                |

| 4       | 4 input             | VN4                |

| 5       | 5 input             | VN5                |

| 6       | 6 input             | VN6                |

| 7       | 7 input             | VN7                |

| 8       | 8 input             | VN8                |

| 9       | 9 input             | VN9                |

| Α       | A input             | VNA                |

| В       | B input             | VNB                |

| С       | C input             | VNC                |

| D       | D input             | VND                |

| Е       | E input             | VNE                |

| F       | F input             | VNF                |

Table 3-8

| Item     | Contents in video mode                | RS-232C/RS-422 CMD |  |  |

|----------|---------------------------------------|--------------------|--|--|

| ABL      | ABL level adjustment                  | VNO                |  |  |

| S. VER   | Shading vertical direction adjustment | VN1                |  |  |

| S. AMP   | Shading amplifier adjustment          | VN2                |  |  |

| S. BAL   | Shading balance adjustment            | VN3                |  |  |

| EB. SW   | Black expansion ON/OFF                | VN4                |  |  |

| COLOR SW | Color switch ON/OFF                   | VN5                |  |  |

| COMBI    | Combination ON/OFF                    | VN6                |  |  |

| MULTI    | Multi mode ON/OFF                     | VN7                |  |  |

| TRIMMING | Trimming mode ON/OFF                  | VN8                |  |  |

Table 3-9

| Item         | Contents in service mode                | RS-232C/RS-422 CMD |  |

|--------------|-----------------------------------------|--------------------|--|

| MONITOR      | Monitor select<br>(Y/B - Y/R - Y/G - Y) | VNO                |  |

| BELL FIL     | Bell adjustment                         | VN1                |  |

| SECAM R - Y  | Black level (R - Y) adjustment          | VN2                |  |

| SECAM B - Y  | Black level (B - Y) adjustment          | VN3                |  |

| SUB CONTRAST | Sub contrast adjustment                 | VN4                |  |

**Table 3-10**

| Item | Contents in special mode | RS-232C/RS-422 CMD |  |  |

|------|--------------------------|--------------------|--|--|

| 0    | RAM area (040-05F)       | VN0                |  |  |

| 1    | RAM area (060-07F)       | VN1                |  |  |

| 2    | RAM area (080-09F)       | VN2                |  |  |

| 3    | RAM area (0A0-0BF)       | VN3                |  |  |

| 4    | RAM area (0C0-0DF)       | VN4                |  |  |

| 5    | RAM area (0E0-0FF)       | VN5                |  |  |

| 6    | RAM area (100-11F)       | VN6                |  |  |

| 7    | RAM area (120-13F)       | VN7                |  |  |

| 8    | RAM area (140-15F)       | VN8                |  |  |

| 9    | RAM area (160-17F)       | VN9                |  |  |

| Α    | RAM area (180-19F)       | VNA                |  |  |

| В    | RAM area (1A0-1BF)       | VNB                |  |  |

| С    | RAM area (1C0-1DF)       | VNC                |  |  |

| D    | RAM area (1E0-1FF)       | VND                |  |  |

| Е    | RAM area (200-21F)       | VNE                |  |  |

| F    | RAM area (220-23F)       | VNF                |  |  |

**Table 3-11**

| ltem<br>UP | Contents in normal mode  Item select UP | RS-232C/RS-422 CMD |     |     |

|------------|-----------------------------------------|--------------------|-----|-----|

|            |                                         | VUP                |     |     |

| DOWN       | Item select DOWN                        | VDW                |     |     |

| LEFT       | Item select LEFT                        | VLF                |     |     |

| RIGHT      | Item select RIGHT                       | VRG                |     |     |

| MEMORY     | Adjusting data write                    | MEM                | MEO | MES |

| ESCAPE     | Item releasing                          | ESC                |     |     |

**Table 3-12**

| Item     | Contents in normal mode  Raster R ON/OFF                        | RS-232C/RS-422 CMD |     |     |

|----------|-----------------------------------------------------------------|--------------------|-----|-----|

| R-ON/OFF |                                                                 | RSW                |     |     |

| G-ON/OFF | Raster G ON/OFF                                                 | GSW                |     |     |

| B-ON/OFF | Raster B ON/OFF                                                 | BSW                |     |     |

| R-SEL    | Raster R selection                                              | SLR                |     |     |

| G-SEL    | Raster G selection                                              | SLG                |     |     |

| B-SEL    | Raster B selection                                              | SLB                |     |     |

| UP       | Adjusting value vertical direction increase/Item select UP      | VUP                |     |     |

| DOWN     | Adjusting value vertical direction decrease/ Item select DOWN   | VDW                |     |     |

| LEFT     | Adjusting value horizontal direction decrease/item select LEFT  | VLF                |     |     |

| RIGHT    | Adjusting value horizontal direction increase/item select RIGHT | VRG                |     |     |

| SPEED    | Adjusting value increase/<br>decreasee speed switching          | VSP                |     |     |

| MEMORY   | Adjusting data write                                            | MEM                | MEO | MES |

| ESCAPE   | Item relasing                                                   | ESC                |     |     |

| FUNCTION | Multi-purpose key                                               | FNC                |     |     |

## SECTION IV CONTROL CIRCUIT

#### 1. OUTLINE

The control circuit board is composed of 3 circuits shown below.

- · Microprocessor circuit

- Internal sync signal generating circuit

- Test pattern generating circuit

The present paragraph explains the details of sync signal generation circuit and test pattern generation circuit. (For the microprocessor circuit, refer to section 3).

### 2. INTERNAL SYNC SIGNAL GENERATION CIRCUIT

#### 2-1. Outline

This is the circuit to generate the horizontal sync signal (fH) and vertical sync signal (fV) to be supplied to the system during no signal mode and the test mode.

The fH can output 7 kinds of frequency, namely 17 kHz, 24 kHz, 31 kHz, 37 kHz, 50 kHz, 70 kHz and 90 kHz corresponding to the convergence adjusting bank, and these frequencies is controlled by the microprocessor.

The fV is a single frequency of 60 Hz.

#### 2-2. Construction

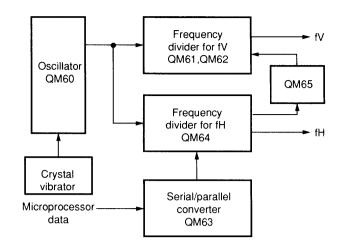

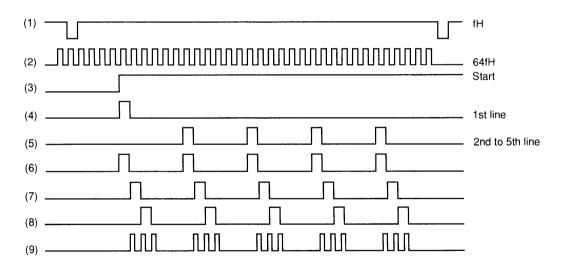

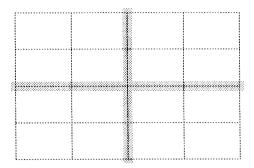

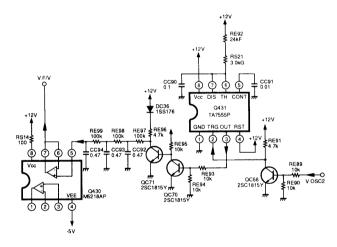

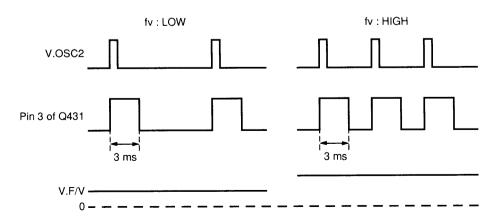

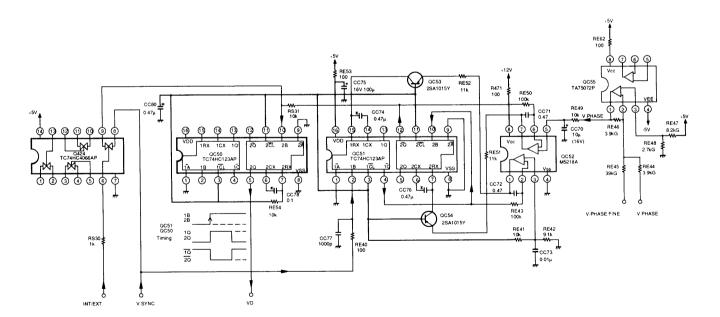

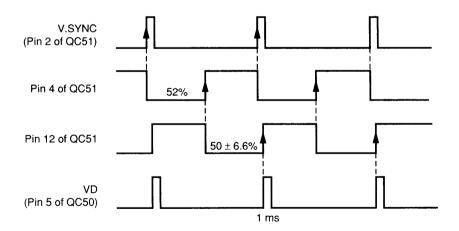

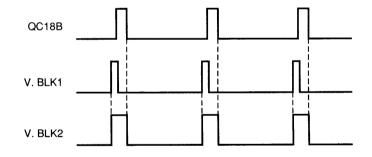

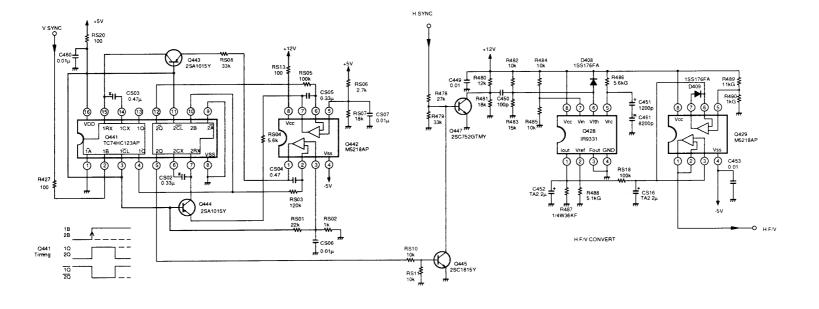

Each frequency of fH and fV is generated by dividing the basic clock of 3.58 MHz respectively. Fig. 2-1 shows this situation.

QM60 is C-MOS.NOT gate, which, together with a crystal vibrator, build up an oscillator. QM61 and QM62 are the frequency dividers for fV, and the frequency division ratio is fixed to 1/59648. On the other hand, QM64 is the frequency divider for fV, and the frequency division ratio is determined by the parallel data of 8 bits given from QM63. QM63 is the serial/parallel conversion IC, and the serial data given from the microprocessor is converted into the parallel data by the IC.

QM65 is a flip-flop and is used to synchronize fH with fV. fV is latched with fH to assort the edge of fV with that of fH. In addition, the frequency divider QM61 is reset at the front edge of fV for keeping the cycle of fV to be constant.

Fig. 4-1 Internal sync signal generation circuit

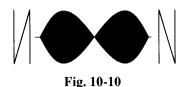

### 3. TEST PATTERN GENERATION CIRCUIT

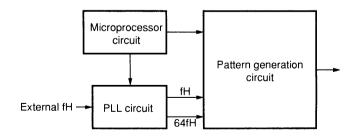

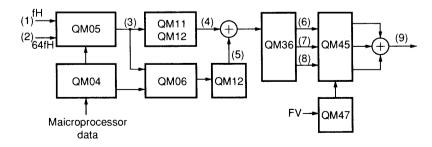

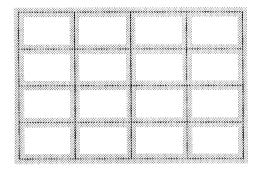

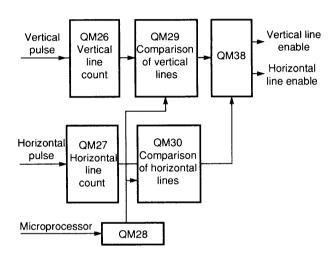

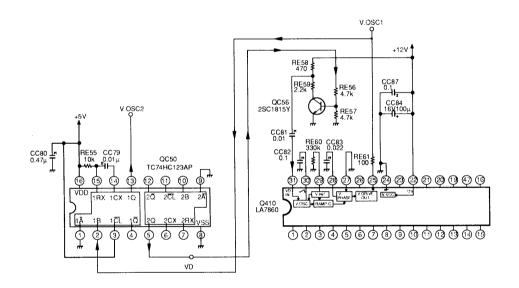

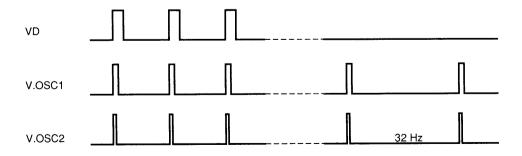

When entering the test mode, the external video sync signal is switched from the internal sync signal described in the preceding Item 2. The test pattern generation circuit outputs various patterns in synchronizing with the internal signal. Fig. 4-2 shows the outline of test pattern generation circuit.

The test pattern generation circuit is composed of the PLL block and the pattern generation block. In PLL block, the internal signal is synchronized and the reference clock (64 fH) of pattern generation is also generated.

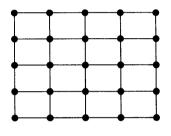

The kinds of pattern that is generated in the pattern generation block are 5 kinds of cross pattern, coarse cross hatch, close cross hatch, H-character and dot. In addition, when adjusting the convergence, it is also possible to display the marker showing the present adjusting point. The details of each circuit are described in the following pages.

Fig. 4-2 Test pattern generation circuit

#### 3-1. PLL Block

#### 3-1-1. Outline

The vertical line of test pattern is formed with the 64 fH as the reference clock. In PLL block, the internal sync signal is synchronized and 64 fH which becomes the system clock of pattern generation circuit is generated. (Refer to Fig. 4-3.)

Fig. 4-3 PLL circuit

#### 3-1-2. Configuration

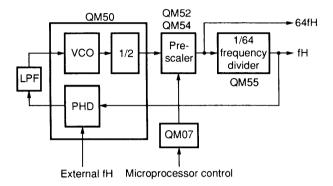

The circuit is composed of the PLL dedicated IC: TLC2932 (QM50) which can build up the PLL with 1 chip. VCO and the phase comparator are accommodated into 1 chip of the IC, and the oscillation range of VCO is within approx. 20 MHz to 70 MHz.

The frequency divider used in the PLL circuit is composed of the pre-scaler and 64-frequency divider. The pre-scaler is composed of QM52 and QM54, and can set 4 kinds of frequency division ratio of 1/2, 1/4, 1/8 and 1/16.

The performance of IC can oscillate up to approx. 70 MHz as described above, but the maximum oscillation frequency is set to around 40 MHz as the EMC countermeasure. VCO output from QM50 (which is already divided into 1/2 frequency inside the IC) is further divided from 1/2 to 1/16 frequency with the pre-scaler. The signal becomes the reference clock of 64 fH.

Further the signal is divided in 1/64 frequency by QM55 and becomes fH. The phase comparator compares fH with the phase of input internal sync signal.

QM54 consisting of the pre-scaler is the buffer equipped with the enable terminal, and selects which signal should be enabled out of 1/2 division to 1/16 division output from the counter (QM52). The division ratio of pre-scaler can be set with the parallel data of 4 bits given from QM07. QM07 is a serial/parallel conversion IC and the data is supplied from the microprocessor.

#### 3-2. Pattern Generation Block

#### 3-2-1. Outline

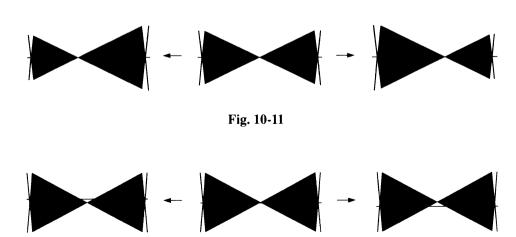

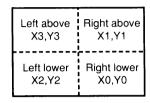

The kinds of pattern generated from the pattern generation block are 5 kinds of cross pattern, coarse cross hatch, close cross hatch, H-character and dot. When adjusting the convergence, the block also generates the marker showing the present adjusting point. These patterns are formed by combining, according to the purpose, the vertical line and horizontal line output from the vertical line generation circuit and horizontal line generation circuit which is as described as follows.

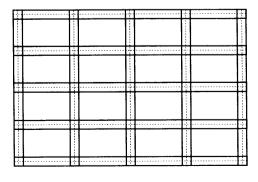

#### 3-2-2. Vertical Line Generation Block

The vertical line of pattern is formed on the basis of the reference clock of 64 fH generated by the PLL circuit. Therefore, what 1H is divided into 64 becomes the minimum unit of vertical line.

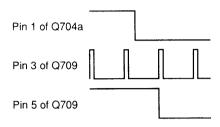

To indicate the vertical line, it is decided first which clock is set to the 1st line (start line). Next, it is decided every how many clock (interval) the line is output. Referring to Figs. 4-4 and 4-5, the circuit operation is explained. QM05 is the counter to set the start line.

- (1) The initial value is loaded with the horizontal sync signal as the reset signal.

- (2) The count operation is started with the 64 fH (2) as a clock.

- (3) Reaching the specified count value, QM05 changes to "H" level from "L" level.

- (4) QM05 signal alone doesn't become the line signal. This signal and a signal delayed by 1 clock in QM12 flip-flop are NORed, and the resultant 1 clock pulse signal is used as a signal for first line.

- (5) QM05 not only decides the position to the 1st line but also makes QM06 for interval count to be the enable state.

- QM06 in the enabled state outputs 1 clock width pulse at every preset interval.

- (6) This pulse signal is combined with the signal (4) after delaying 1 clock with the flip-flop of QM12-2, and then formed the vertical line signal pulse. The starting position and interval data are given to QM05 and QM06 from the serial/parallel conversion IC (QM04).

The pattern generation circuit can also output the convergence adjusting marker. The marker is of square shape which surrounds the cross point of cross hatch pattern.

The vertical line forming the marker uses the lines before and after 1 clock of cross hatch pattern. The vertical line generation circuit forms the vertical line for marker at the same time. Namely, the circuit forms the line with 3 lines/set against 1 line.

(7) The procedure to form the line of 3 lines/set is as follows:

The pattern position signal formed in (6) is input to the shift register QM36 and the pattern position signal of 3 different kinds of phase is extracted.

The first phase signal (6) corresponds to the left line of marker and the second phase signal (7) to the cross hatch signal. Next, the third phase signal (8) corresponds to the right line of marker.

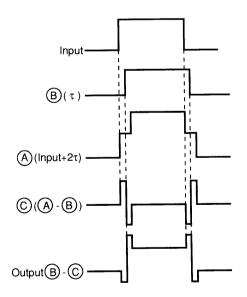

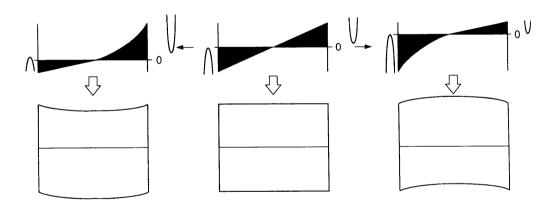

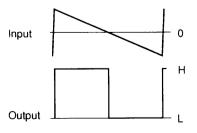

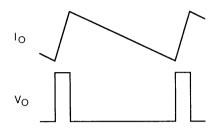

(8) The pulse of pattern position signal as mentioned above has 1 clock width of system clock (64 fH) of pattern generation circuit. When the signal is projected to a large type screen like a projector, it becomes a considerably thick pattern. A fine pattern (9) is created by differentiating the pattern signal obtained there. The differentiation circuit is formed with the circuit consisting of QM45 as its center. The OP amp. QM47 gives the offset to the signal which is differentiated on the basis of the FV conversion voltage given from the microprocessor. Thereby, the threshold of differentiation waveform vertically moves according to the frequency of input signal so that the pattern having a constant thickness at all times is obtained (9).

Fig. 4-4 Timing chart

Fig. 4-5 Vertical line generation circuit

#### 3-2-3. Horizontal Line Generation Block

The horizontal line generation circuit is basically identical to the vertical line generation circuit. What differs from the latter is to use the horizontal 1 line to form the line instead of using the clock signal. The horizontal line generation circuit counts the number of horizontal lines. Further, when forming the horizontal line above and below the marker, the former uses the fore and after lines having the space of 1/8 the pattern interval instead of using the line before and after 1 line.

This is for making the apparent marker size to be constant even if the signals of various line numbers is input. The pattern start position is set to the counter composed of QM14 and QM15, and the pattern interval is set to the counter composed of QM23 and 24. QM21 is the counter to form the space of 1/8 the pattern interval.

The vertical line is also formed with 3 lines/set.

#### 3-2-4. Cross Hatch Pattern

This is the circuit to output the cross hatch necessary to adjust the convergence. The cross hatch pattern is formed by the logical OR of each center line of 3 lines/set that obtained by the vertical and horizontal line generation circuit. The cross hatch pattern can output the coarse cross hatch of  $5 \times 5$  and the close cross hatch of  $13 \times 11$ .

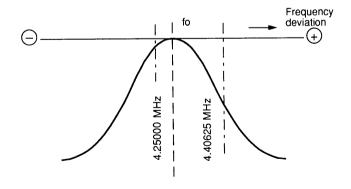

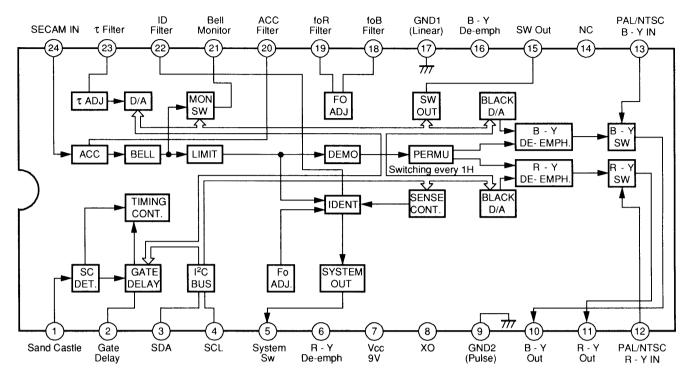

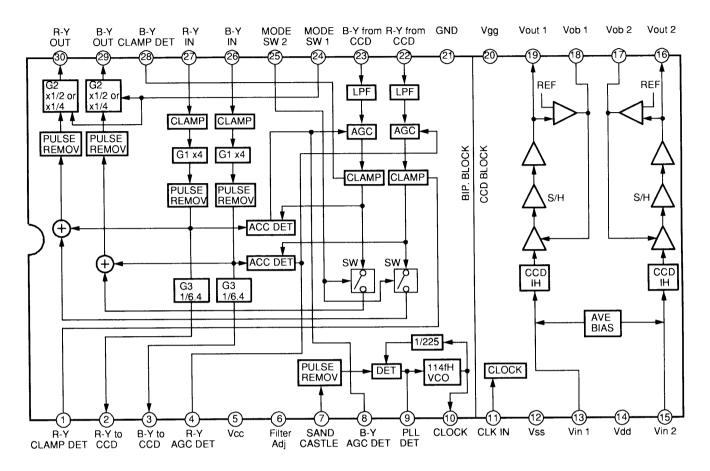

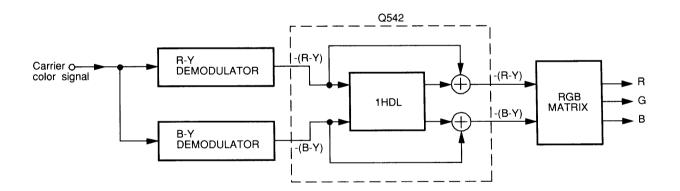

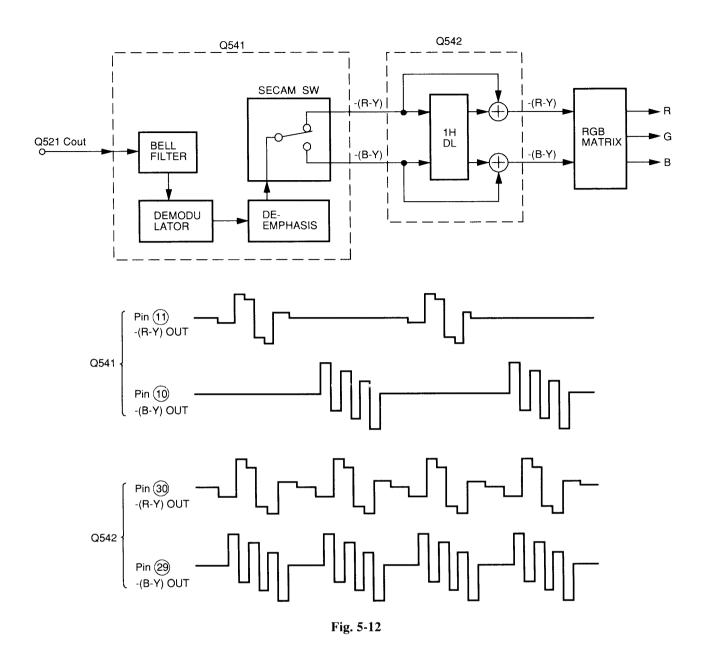

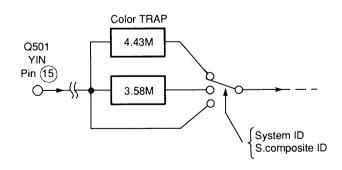

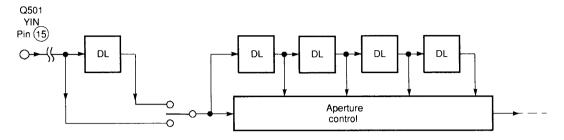

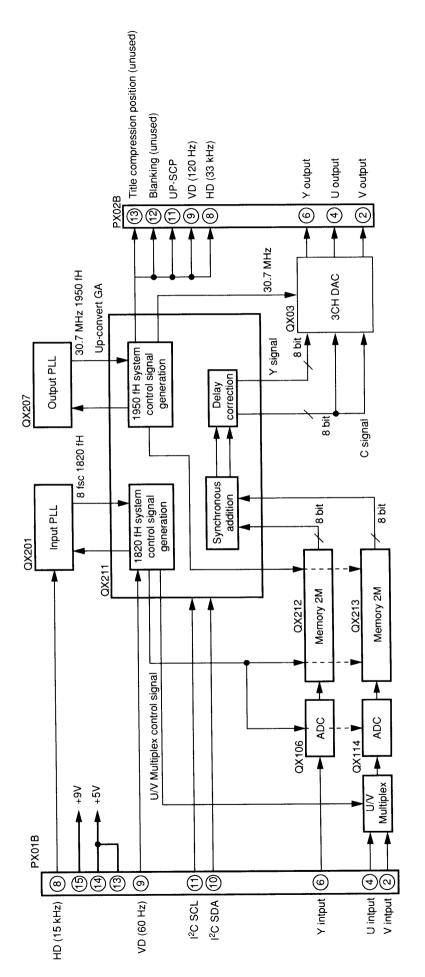

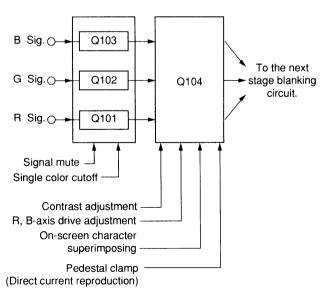

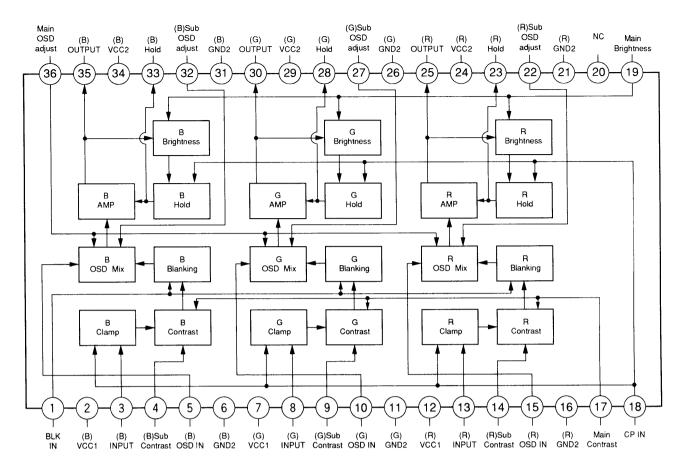

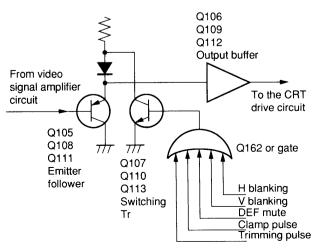

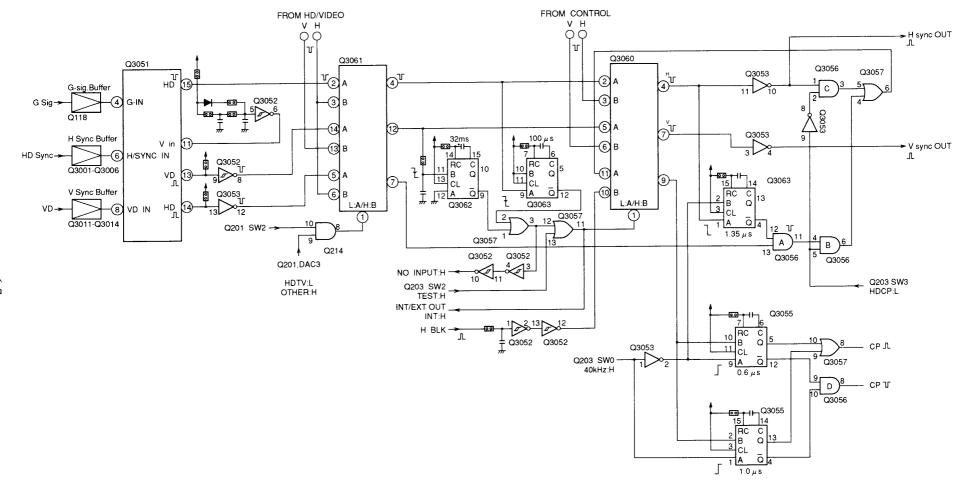

The horizontal line is formed with 1 scanning line as earlier described. Which line should be set to the 1st line of cross hatch with the vertical sync signal as the reference is the pattern start position data. In addition, every how many line the line should be output with the pattern start position is the pattern interval data. The number of scanning lines varies with the frequency of signal input. Therefore, these start position data and interval data need to set the adequate data for every bank of convergence adjusted.